ASML“掀老底”,称3nm芯片实际为23nm,我们竟被芯片企业营销了

如何评价网传 ASML「掀老底」称 3nm 芯片实际为 23nm,1nm 芯片是 18nm?近日,ASML在公布自己的EUV光刻机路线图时,更是将各大晶圆厂的老底掀开了,ASML的PPT,非常清楚的指出了各大晶圆工艺,对应的金属半节距,如果按照最开始芯片工艺的说法,这个才是实际的芯片工艺。如上图所示,N3(3nm工艺)对应的是23nm,N2(2nm工艺)对应的是22nm,A14(1.4nm工艺)对应的是21nm。A10也就是1nm时,对应的是18nm,A7也就是0.7nm时,应对的是18-16nm,甚至到A2,也就是0.2nm时,实际金属半间距是16-12nm。

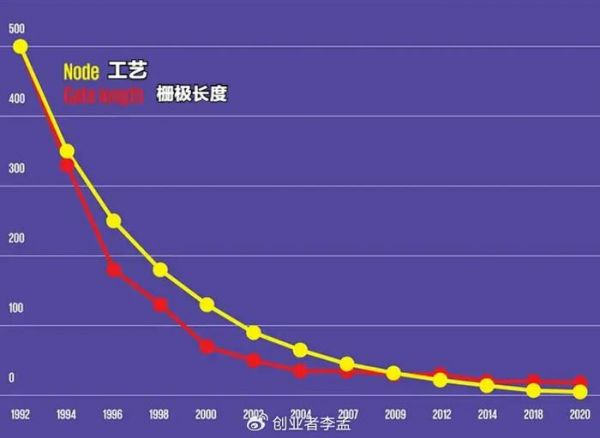

在评价这个问题之前,我们需要了解一下背景知识。半导体工艺节点的命名,如7nm、5nm、3nm等,并不直接对应实际的物理尺寸,而是行业内约定俗成的一种命名方式。这些数字大致反映了晶体管的密度和性能水平,但并不是严格的几何度量。随着工艺技术的进步,这种命名与实际物理尺寸之间的差异变得越来越大。

ASML作为全球领先的光刻机制造商,其公布的EUV光刻机路线图和晶圆工艺数据具有很高的参考价值。这些数据揭示了实际芯片工艺与宣传工艺之间的差距,对于了解半导体行业的真实情况具有重要意义。ASML的曝光事件对全球芯片行业产生了显著影响,特别是对于那些依赖ASML先进光刻机的公司。

根据ASML的PPT,我们来复盘总结下关键数据:

N3(3nm工艺)实际对应的金属半节距为23nm。N2(2nm工艺)实际对应的金属半节距为22nm。A14(1.4nm工艺)实际对应的金属半节距为21nm。A10(1nm工艺)实际对应的金属半节距为18nm。A7(0.7nm工艺)实际对应的金属半节距为18-16nm。A2(0.2nm工艺)实际对应的金属半节距为16-12nm。

从这些数据中,我们可以得出以下几点结论:

1、实际芯片工艺与宣传工艺之间存在差距。这可能是因为宣传工艺是基于晶体管的物理尺寸,而实际工艺受到多种因素的影响,如光刻机的分辨率、材料的性质等。

2、随着工艺的进步,实际工艺与宣传工艺之间的差距逐渐缩小。这表明随着技术的发展,半导体行业正在逐步克服各种技术难题,提高芯片的制造精度。随着技术的发展,实现更小制程的技术难度呈指数级增长。为了继续推进摩尔定律,工程师们不得不采用越来越复杂的设计和制造技术,这导致了实际物理尺寸与工艺节点名称之间的差距。

3、尽管存在差距,但半导体行业仍在不断努力推动工艺的发展。从3nm到1nm,再到0.7nm和0.2nm,每一次工艺的进步都代表着人类对微观世界的探索又向前迈进了一步。

4、工艺节点命名的抽象性,我们发现工艺节点的名称更多是一个市场营销术语,而不是精确的科学度量。这种命名方式有助于消费者理解不同代技术的相对进步,但也可能导致误解。

5、行业透明度,ASML公开这样的信息可能是为了提高行业透明度,让客户和市场更加清晰地了解不同工艺节点的实际技术水平。这也可能有助于调整市场对先进工艺的期望。

6、对竞争的影响,这种信息的公开可能会影响不同半导体制造商之间的竞争,因为它揭示了谁真正领先于技术创新和谁可能在营销上过于夸大其词。

总结整理后,我们会发现,ASML公布的这些数据揭示了半导体行业的真实情况,虽然实际工艺与宣传工艺之间存在差距,但这并不妨碍行业内的技术进步和发展。对此大家是怎么看的,欢迎关注我创业者李孟和我一起交流!

发布于:陕西

相关推荐

ASML“掀老底”,称3nm芯片实际为23nm,我们竟被芯片企业营销了

ASML掀开台积电的老底,28纳米以后的芯片工艺升级都是假的!

芯片“暴利”江湖

芯片制程之战:三星台积电挺进3nm,英特尔们呢?

芯片制程:28nm向3nm的“大跃进”

3nm的芯片战争,才刚刚开始

2024,中国芯片想要突破卡脖子,还需要什么?

3nm备战进入倒计时

差距进一步扩大?ASML第三代EUV光刻机交付,用于2nm芯片报价约13亿元

台积电、三星的3nm实际良率都只有50%左右!

网址: ASML“掀老底”,称3nm芯片实际为23nm,我们竟被芯片企业营销了 http://www.xishuta.com/newsview120971.html

推荐科技快讯

- 1问界商标转让释放信号:赛力斯 94951

- 2人类唯一的出路:变成人工智能 19220

- 3报告:抖音海外版下载量突破1 18936

- 4移动办公如何高效?谷歌研究了 18463

- 5人类唯一的出路: 变成人工智 18321

- 62023年起,银行存取款迎来 10125

- 7网传比亚迪一员工泄露华为机密 8179

- 8顶风作案?金山WPS被指套娃 7096

- 9大数据杀熟往返套票比单程购买 7045

- 10五一来了,大数据杀熟又想来, 6834