杀疯了的CoWoS

来源:半导体行业观察

因为CoWoS 高级封装在人工智能加速器的开发中扮演着至关重要的角色。于是,台积电正在大力提高这个技术的产能。

最近,有消息指出,台积电目前的 CoWoS 产能据说是每月 36000片,这家台湾巨头的目标是到明年年底将这一数字提高到 90000 片。如果台积电继续按计划升级设备和建造新设备,该公司的目标是到 2026 年将 CoWoS 的产量提高到 130000片,即在短短一年内将产量提高近 4 倍。与此同时,这家台湾巨头还将提高 CoWoS 的价格,以满足扩产所需的成本。

当然,在技术方面,台积电也与时俱进。

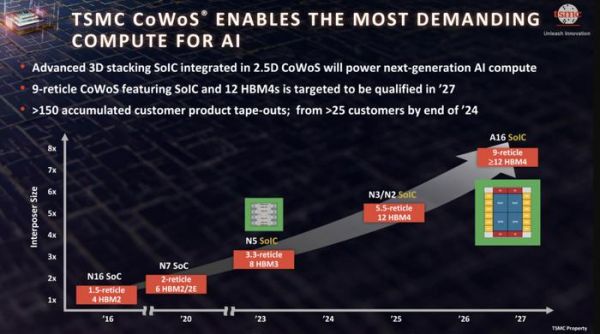

台积电“超级载体” CoWoS

台积电本月在其欧洲开放创新平台 (OIP) 论坛上宣布,该公司有望在 2027 年实现其超大版晶圆上芯片 (CoWoS) 封装技术的认证,该技术将提供高达九个光罩(reticle)尺寸的中介层和 12 个 HBM4 内存堆栈。新的封装方法将满足对性能要求最高的应用,并让 AI 和 HPC 芯片设计人员能够构建手掌大小的处理器。

台积电每年都会推出新的工艺技术,尽最大努力满足客户对功率、性能和面积 (PPA) 改进的需求。但有些客户需要更高的性能,而 858 平方毫米的 EUV 光刻工具掩模版限制对他们来说不够。这些客户选择使用台积电 CoWoS 技术封装的多芯片解决方案,近年来,该公司提供了该方法的多次迭代。

最初的 CoWoS 在 2016 年实现了约 1.5 倍掩模版大小的芯片封装,然后发展到今天的 3.3 倍掩模版大小,可以将八个 HBM3 堆栈放入一个封装中。接下来,台积电承诺在 2025 年至 2026 年推出 5.5 倍掩模版大小的封装,最多可容纳 12 个 HBM4 内存堆栈。然而,这比该公司的终极版 CoWoS 逊色不少,后者可实现多达九倍掩模版大小的系统级封装 (SiP),板载 12 个甚至更多的 HBM4 模块。

该款 9 光罩 “超级载体”('Super Carrier' )CoWoS(为芯片和内存提供高达 7,722 平方毫米的空间)配有 12 个 HBM4 堆栈,计划于 2027 年获得认证,因此有理由预计它将在 2027 年至 2028 年间被超高端 AI 处理器采用。

台积电完全相信采用其先进封装方法的公司也会使用其系统级集成芯片 (SoIC) 先进封装技术垂直堆叠逻辑,以进一步提高晶体管数量和性能。事实上,借助 9 光罩 CoWoS,台积电预计其客户会将 1.6nm 级芯片放置在 2nm 级芯片之上,因此我们谈论的是极高的晶体管密度。

然而,这些超大型 CoWoS 封装面临着重大挑战。5.5 掩模版 CoWoS 封装将需要超过 100x100 毫米的基板(接近 OAM 2.0 标准的尺寸限制,尺寸为 102x165 毫米),而 9 掩模版 CoWoS 将超过 120x120 毫米的基板。如此大的基板尺寸将影响系统的设计方式以及数据中心如何配备以支持它们。特别是电源和冷却。说到电源,我们谈论的是每个机架数百千瓦,而说到冷却,我们谈论的是液体冷却和浸没式方法,以有效管理高功率处理器。

CoWOS技术是什么?

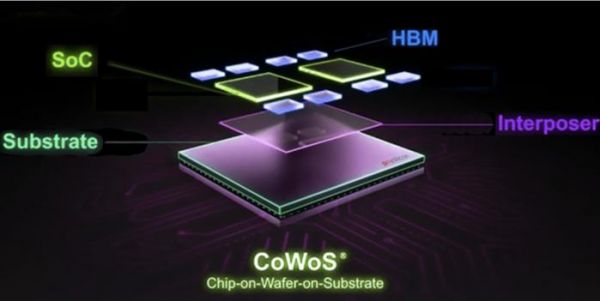

晶圆上芯片 (CoWoS:Chip-on-wafer-on-substrate)是一种先进的封装技术,具有封装尺寸更大和 I/O 连接更多等优势。它允许 2.5D 和 3D 组件堆叠,以实现同质和异构集成。以前的系统面临内存限制,而当代数据中心则使用高带宽内存 (HBM) 来增强内存容量和带宽。CoWoS 技术允许在同一 IC 平台上异构集成逻辑 SoC 和 HBM。

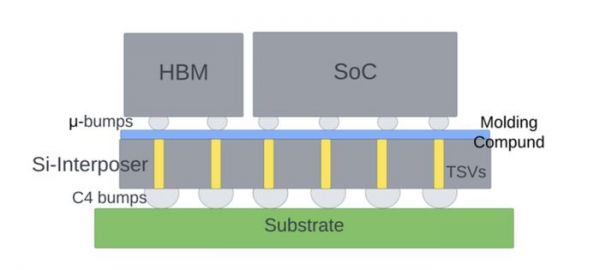

CoWoS 架构包含 2.5D 水平堆叠和 3D 垂直堆叠配置,彻底改变了传统的芯片封装模式。这种创新方法允许逐层堆叠各种处理器和内存模块,从而创建相互连接以形成一个有凝聚力的系统的小芯片。通过利用硅通孔 (TSV) 和微凸块,与传统的 2D 封装方法相比,CoWoS 可以缩短互连长度、降低功耗并增强信号完整性。

从实际角度来看,CoWoS 技术能够将 GPU 和 AI 加速器等高级处理单元与高带宽内存 (HBM) 模块无缝集成。这种集成对于 AI 应用尤其重要,因为在这些应用中,大规模计算能力和快速数据访问至关重要。通过将处理和内存元件放在近距离内,CoWoS 可以最大限度地减少延迟并最大限度地提高吞吐量,从而为内存密集型任务带来前所未有的性能提升。

CoWoS 技术具有多种优势:

规模化和更高集成度:传统上,按照摩尔定律对晶体管进行规模化有助于满足提高性能的需求。然而,事实证明,这对于高性能计算 (HPC)、人工智能甚至图形处理单元 (GPU) 等现代应用而言是不够的。CoWoS 允许在同一基板上堆叠芯片,从而减少同质或异构逻辑 SoC 之间以及 HBM 之间的互连延迟。

增强热管理:硅中介层和有机中介层的使用大大增强了堆叠集成电路的热管理能力。这直接提高了整个系统的可靠性和使用寿命,同时最大限度地降低了热节流的风险。

提高电源完整性:中介层中的电源/接地网络使用 RDL,并结合深槽电容器 (DTC),不会损害高速应用和内存密集型应用的电源完整性。

尺寸和成本降低: CoWoS 技术有助于在同一中介层和基板上安装多个逻辑 SoC 和 HBM。这与传统封装技术形成鲜明对比,传统封装技术过去需要将多个逻辑 SoC 安装在印刷电路板 (PCB) 上,并在封装中进行必要的连接。这导致封装尺寸更大,并增加了材料成本和制造费用。CoWoS 封装总体上更小,更具成本效益。

CoWOS的三种技术变体

据介绍, 目前有CoWoS-S、CoWoS -L 和 CoWoS -R三个平台。不同的互连选项提供更大的灵活性集成,以满足性能目标。

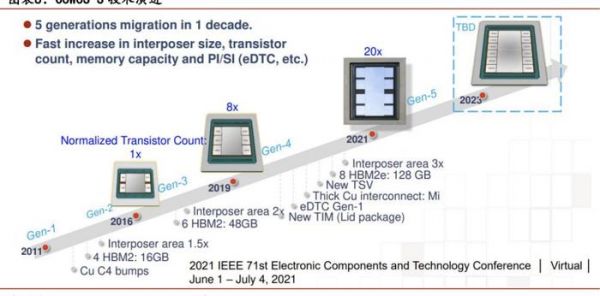

据中邮证券的报告,CoWoS-S(Silicon Interposer)即 2011 年首次亮相的用硅(Si)衬底作为中 介 层 的 先 进 封 装 技 术 ( chip-on-wafer-on-substrate with silicon interposer)和TSV,提供广泛的中介层尺寸、HBM 立方体数量和封装尺寸,可以实现大于 2X 的光罩尺寸(1,700mm2),中介层集成了领先的 SoC 芯片和四个以上的HBM2/HBM2E 立方体。在过去,“CoWoS”一般即指以硅基板作为中介层的先进封装技术。

报告进一步指出,CoWoS-S 从 2011 年的第一代升级到 2021 年的第五代,后续的第六代技术将会在基板上封装 2 颗运算核心,同时可以板载多达 12 颗 HBM 缓存芯片。第五代 CoWoS-S 技术使用了全新的 TSV 解决方案,更厚的铜连接线,晶体管数量是第 3 代的 20 倍。它的硅中介层扩大到 2500mm2,相当于 3 倍光罩面积,拥有 8 个 HBM2E 堆栈的空间,容量高达 128 GB。并且,台积电以 Metal Tim形式提供最新高性能处理器散热解决方案,与第一代 Gel TIM 相比,封装热阻降低至 0.15 倍。

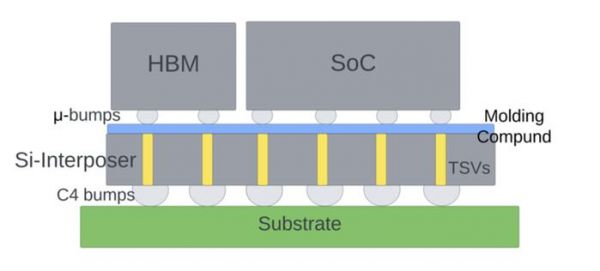

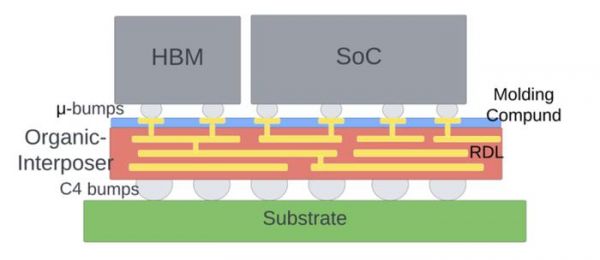

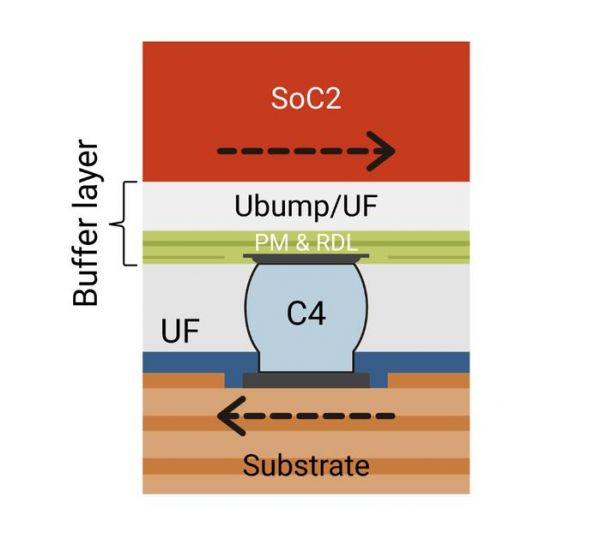

CoWoS-R则使用有机中介层取代了 CoWoS-S 的硅中介层。有机中介层具有细间距 RDL,可在 HBM 和芯片之间甚至芯片和基板之间提供高速连接。与 CoWoS-S 相比,CoWoS-R 提供了卓越的可靠性和良率,因为有机中介层本身具有柔韧性,可充当应力缓冲器,并减轻由于基板和中介层之间的热膨胀系数不匹配而引起的可靠性问题。

按照台积电所说,CoWoS -R 的主要特点包括:

1、用于布线的 RDL 中介层最多包含 6 个铜层,间距最小为 4μm(线宽/间距为 2μm)。

2、RDL 互连提供良好的信号和电源完整性,并采用较低的 RC 值布线,以实现高数据传输率。共面接地-信号-接地-信号-接地 (GSGSG) 和具有六个 RDL 互连的层间接地屏蔽可提供卓越的电气性能。

3、由于 SoC 和相应基板之间的热膨胀系数 (CTE) 不匹配,RDL 层和 C4/底部填充 (UF) 层提供了出色的缓冲。C4 凸块区域的应变能量密度大大降低。

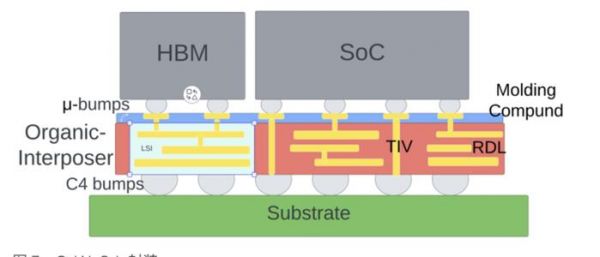

CoWoS-L则使用局部硅互连 (LSI) 和 RDL 中介层一起形成重组中介层 (RI)。除了 RDL 中介层之外,它还以硅通孔 (TSV) 的形式保留了 CoWoS-S 的吸引力。这还可以缓解由于在 CoWoS-S 中使用大型硅中介层而产生的产量问题。在一些实现中,它还可以使用绝缘通孔 (TIV) 代替 TSV 来最大限度地减少插入损耗。

CoWoS -L 的主要特点包括:

1、LSI 芯片用于通过多层亚微米铜线实现高布线密度芯片间互连。LSI 芯片可以在每个产品中采用各种连接架构,例如片上系统 (SoC) 到 SoC、SoC 到芯片组、SoC 到高带宽内存,并且可以在多种产品中重复使用。相应的金属类型、层数和间距与 CoWoS -S 的产品一致。

2、基于成型的中介层在正面、背面和传输信号和电源的 InFO 通孔 (TIV) 上具有较宽的 RDL 层间距,可在高速传输过程中降低高频信号的损耗。

3、能够在 SoC 芯片下方集成独立嵌入式深沟槽电容器等附加元素,以改善电源管理。

总而言之,CoWoS-L 是一种芯片后组装工艺,因为先制造中介层,然后再在上面堆叠晶圆芯片。中介层是 CoWoS 技术中的关键原材料之一,因为中介层上安装了多个晶圆芯片(如 SoC、HBM 等),并且它能够实现芯片之间的高效连接和通信。中介层制造完成后,下一步就是在晶圆芯片中创建绝缘通孔 (TIV)。

然后将已知合格的裸片 (KGD) 安装在晶圆上。裸片和 TIV 之间的间隙用模塑料填充,然后采用 CMP 工艺获得平坦表面。

下一步,制造两个 RDL 层:一个位于中介层正面,通过 μ-bump 连接晶圆和基板。

中介层背面的第二条 RDL 通过 C4 凸块连接中介层和基板。

除此之外,CoWoS-L 技术还采用深沟槽电容器 (DTC),可提供高电容密度,从而提高系统的电气性能。这些电容器充当电荷储存器,并在运行高速计算应用程序时满足瞬时电流需求。

面临的挑战

与系统级芯片 (SiP) 等旧式封装技术相比,CoWoS 技术可以在一个封装中支持更多数量的晶体管。所有需要大量并行计算、处理大量数据向量以及需要高内存带宽的应用程序都最适合使用此技术。

CoWoS的一些应用包括:高性能计算 (HPC)、人工智能(AI)和机器学习(ML)、网络和数据中心以及图形处理单元 (GPU) 和游戏。

但COWOS面临着多方面的挑战:

1、制造复杂性和成本考虑: CoWoS 是一种 2.5D/3D 集成技术,与前代技术相比,制造复杂性显著增加。制造复杂性直接导致采用这种封装技术的芯片成本增加。这被认为是近年来 HPC 和 AI 芯片成本增加的一个重要原因。测试 CoWoS 的成本也会增加总成本。

2、集成和良率挑战: 5D 和 3D 集成电路需要像任何其他集成电路一样进行测试,以确保它们没有任何制造缺陷。然而,测试 2.5D 或 3D 集成电路要困难得多,因为每个晶圆芯片在安装到中介层之前都需要单独测试,安装后还需要再次测试。除此之外,硅通孔 (TSV) 也需要测试。最后,大型硅中介层特别容易受到制造缺陷的影响,并可能导致良率损失。

3、散热挑战:由于中介层和基板之间的热膨胀系数 (CTE) 不同,CoWoS 封装会遇到散热问题。使用有机中介层确实可以在一定程度上限制散热问题。使用底部填充材料可以缓冲硅片和基板之间的热失配,从而大大提高焊点的寿命。

同样,在正面,重分布层 (RDL) 的完整性(尤其是两个硅片下方的重分布层)容易受到应力影响。μ-bump 底部填充材料再次充当了硅片和 RDL 之间的应力缓冲层。

4、电气挑战: CoWoS 封装面临着信号和电源完整性问题等电气挑战。

(1)信号完整性:

逻辑晶圆芯片到基板的互连:随着数据速率的提高,由于 TSV 的寄生电容和电感,互连的信号传输会变差。为了解决这个问题,人们努力优化 TSV,以最大限度地降低电容和电感。

逻辑晶圆芯片到 HBM:SoC 和 HBM 之间互连的眼图性能瓶颈归因于互连的寄生电阻和电容。

(2)电源完整性:CoWoS 封装通常用于具有较高数据切换率和较低工作电压的高性能应用。这使得这些封装容易受到电源完整性挑战。

CoWoS 技术提供更高水平的集成,使集成电路能够扩展以满足不断增长的计算能力的需求。该技术不断发展,以确保更好的产量、强大的功率和热完整性,并进一步增加中介层面积,以允许更多晶圆共享同一基板。CoWoS 将在未来几年继续推动半导体行业的发展。

参考链接

https://www.tomshardware.com/tech-industry/tsmc-super-carrier-cowos-interposer-gets-bigger-enabling-massive-ai-chips-to-reach-9-reticle-sizes-with-12-hbm4-stacks

https://anysilicon.com/cowos-package/

相关推荐

杀疯了的CoWoS

击败Tiktok,吊打网飞,中国“霸总”爽剧在欧美杀疯了?

造车杀疯了:大家连IPO都想好了

杀疯了!收入暴增,一天15亿

“杀疯了”的剧本杀,如何敲开年轻人的门?

中国“土味”短剧,在美国杀疯了

台积电CoWoS先进封装产能告急!

挤牙膏的英特尔,也有“杀疯了”的一天?

剧本杀“杀疯了”,个人投资者纷纷进入市场,赚钱却不是那么容易

中国「土味」短剧,在美国杀疯了

网址: 杀疯了的CoWoS http://www.xishuta.com/newsview129264.html

推荐科技快讯

- 1问界商标转让释放信号:赛力斯 94843

- 2人类唯一的出路:变成人工智能 18334

- 3报告:抖音海外版下载量突破1 17915

- 4移动办公如何高效?谷歌研究了 17601

- 5人类唯一的出路: 变成人工智 17439

- 62023年起,银行存取款迎来 10018

- 7网传比亚迪一员工泄露华为机密 8016

- 8顶风作案?金山WPS被指套娃 6501

- 9大数据杀熟往返套票比单程购买 6477

- 1012306客服回应崩了 12 6379