芯片制程之战:三星台积电挺进3nm,英特尔们呢?

本文来自微信公众号:智东西(ID:zhidxcom),作者:心缘,题图来自:视觉中国

2020年开篇伊始,全球半导体先进制程之战新的交锋已然火花四射。

从华为、苹果打响7nm旗舰手机芯片第一枪开始,7nm芯片产品已成百花齐放之势,而5nm芯片也将在今年下半年正式首秀。

10nm、7nm、5nm、3nm……这些逐渐缩小的芯片制程数字,正是全球电子产品整体性能不断进化的核心驱动力。通往更先进制程的道路犹如攀登高峰,飙高的技术难度和研发成本将大多数芯片代工厂拦在半山腰,全球唯有台积电、三星、英特尔还在向峰顶冲刺。

就在刚刚过去4个月,三星、台积电和英特尔接连密集释放关于更先进制程的新讯息。

三星首款3nm芯片研发成功,台积电3nm芯片晶体管密度达2.5亿/mm²,英特尔官宣制程回归两年更新周期。

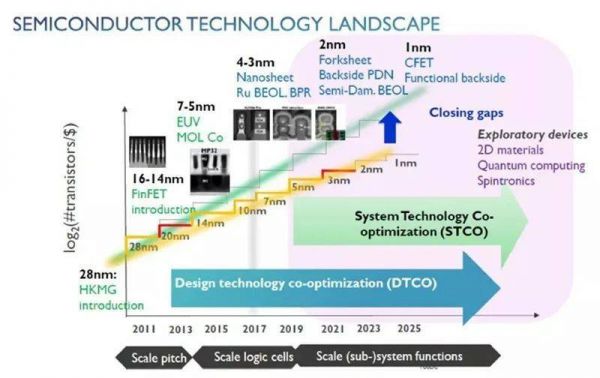

全球主要晶圆厂制程节点技术路线图

与此同时,作为过去十年芯片制程演进的关键功臣,FinFET之父、美国加州大学伯克利分校教授胡正明被授予国际电气与电子工程学会2020年IEEE荣誉勋章。

在全球备战3nm及更先进制程的关键节点,本文围绕晶体管结构、光刻、沉积与刻蚀、检测、封装等五大关键环节,探讨全球先进制程冲刺战中更高阶的核心技术及玩家格局。

迈向1nm节点的技术路线图(图源:Imec)

一、世界上最烧钱长跑:芯片制程进阶之路

什么是芯片制程?制程用来描述芯片晶体管栅极宽度的大小,纳米数字越小,说明晶体管密度越大,芯片性能就越高。

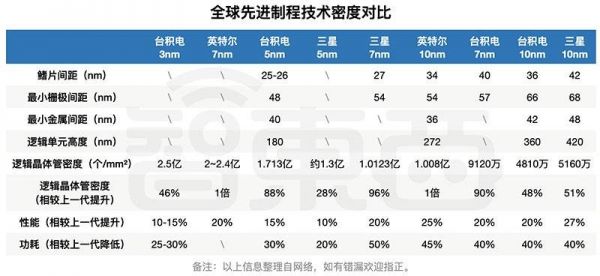

例如,台积电7nm芯片的典型代表苹果A13、高通骁龙865和华为麒麟990,每平方毫米约有1亿个晶体管。随后台积电5nm、3nm芯片进一步将每平方毫米的晶体管数量提升至1.713亿个、2.5亿个。

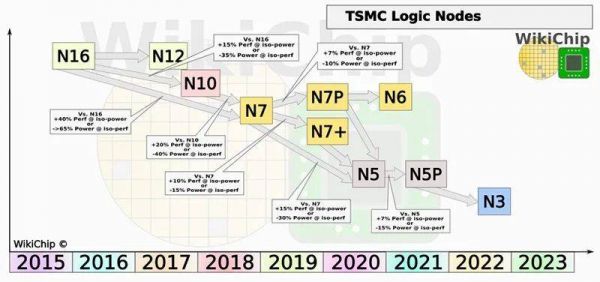

台积电制程工艺节点路线图(图源:WikiChip)

伴随着制程的进化,5nm比7nm芯片性能提升15%,功耗降低30%;3nm又比5nm芯片性能提升10%~15%,功耗降低25%~30%。

由于各家对制程工艺的命名法则不同,相同纳米制程下,并不能对各厂商的制程技术进展做直观比较。比如英特尔10nm的晶体管密度与台积电7nm、三星7nm的晶体管密度相当。

全球先进制程技术对比

从制程最新进展来看,一边是台积电、三星在5nm/3nm等先进制程上你追我赶,另一边英特尔则韬光养晦,循序渐进地走向7nm。

5nm方面,台积电已经拿到苹果和华为的旗舰手机芯片订单,下半年开启量产,有望在其2020年营收中占比达10%。

三星在5nm制程则相对落后,目前正加速韩国华城5nm生产工厂V1的建设,预计6月底前完成生产线建设,今年年底前实现量产。

据外媒报道,三星与谷歌正合作开发采用三星5nm LPE工艺的定制Exynos芯片组,将搭载于谷歌的Pixel智能手机、Chrome OS设备甚至数据中心服务器中。

3nm方面,台积电3nm制程预计2021年开始试生产,并于2022年下半年开始量产。三星原计划2021年大规模量产3nm工艺,但受当前疫情影响,不确定量产时间是否会推迟。

为什么挺进先进制程的玩家屈指可数呢?主要源于两大门槛:资本和技术。

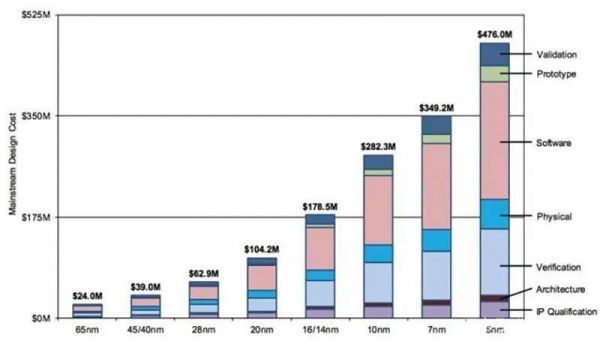

制程工艺的研发和生产成本逐代上涨。根据市场研究机构International Business Strategies(IBS)的数据,3nm芯片的设计费用约达5亿~15亿美元,兴建一条3nm产线的成本约为150亿~200亿美元。

两年前台积电为3nm工艺计划投资6000亿新台币,折合近200亿美元。单是从资金数目来看,很多中小型晶圆厂就玩不起。

不同工艺下的典型芯片流片成本图,28nm后成本开始迅速上升

更高的研发和生产成本,对应的是更难的技术挑战。

每当制程工艺逼近物理极限,晶体管结构、光刻、沉积、刻蚀、检测、封装等技术的创新与协同配合,对芯片性能天花板的突破起到决定性作用。

二、摩尔定律的续命关键:晶体管结构从FinFET走向GAA

晶体管在芯片中起到“开关”作用,能通过影响相互的状态传递信息。晶体管的栅极控制着电流能否从源极流向漏极,电子流过晶体管相当于“开”,电子不流过晶体管相当于“关”。

随着晶体管尺寸缩小,源极和栅极间的沟道不断缩小,当沟道缩短到一定程度时,即便不加电压,源极和漏极也因间距过小而互通,即产生“漏电”现象,晶体管则失去“开关”的功能,无法实现逻辑电路。

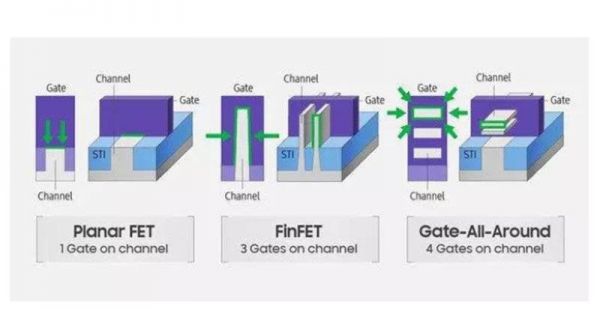

晶体管结构进化路线图

1. 从平面晶体管到FinFET

几十年来,基于平面(Planar)晶体管的芯片一直是市场上最先进的设备。然而制程技术发展到22nm以下节点后,平面晶体管开始遇到源极漏极间距过近的瓶颈。

此时,华裔科学家胡正明教授于1999年发明的3D鳍式场效晶体管(FinFET),成为延续摩尔定律的革命性技术,在过去十年间,为基于逻辑的工艺技术创新做出了核心贡献。

英特尔在2011年转向22nm FinFET。FinFET的立体构造将漏极和源极由水平改为垂直,沟道被栅极三面环绕,不仅增厚绝缘层,而且增加接触面积,避免漏电现象的发生。

相比平面晶体管,FinFET在工艺节点减小时,能做到更好的性能和电压缩放,切换速度和电流密度均显著提升。

从平面晶体管到FinFET再到GAAFET的演变

FinFET已经历16nm/14nm和10nm/7nm两个工艺世代,今年采用台积电5nm FinFET晶体管工艺的芯片预计将在下半年问世。

在衡量技术成熟度、性能和成本等因素后,台积电的3nm首发沿用FinFET晶体管方案。

2. GAAFET:走向3nm及更先进工艺

随着深宽比不断拉高,FinFET逼近物理极限,为了制造出密度更高的芯片,环绕式栅极晶体管(GAAFET,Gate-All-Ground FET)成为新的技术选择。

三星、台积电、英特尔均引入GAA技术的研究,其中三星已经先一步将GAA用于3nm芯片。

不同于FinFET,GAAFET的沟道被栅极四面包围,沟道电流比三面包裹的FinFET更加顺畅,能进一步改善对电流的控制,从而优化栅极长度的微缩。

三星3nm采用的GAA技术名为多桥通道FET(MBCFET,Multi-Bridge Channel FET)。这是一种纳米片FET(nanosheet FET),可通过用纳米片替换纳米线周围的栅极,实现每堆更大的电流。

不过纳米片FET当下还面临一些挑战,包括n/p不平衡、底部板的有效性、内部间隔、栅极长度控制和器件覆盖。

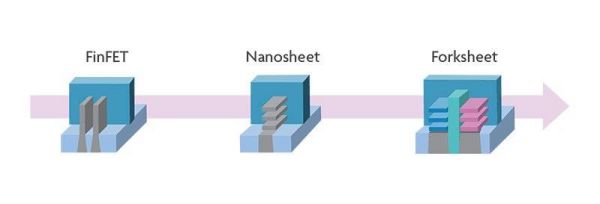

从FinFET到Nanosheet再到Forksheet的演变

微电子研究中心(Imec)正在开发面向2nm的forksheet FET。

与nFET和pFET使用不同器件的现有GAAFET不一样的是,在forksheet FET中,nFET和pFET都集成在同一结构中,间距更小并减少密集缩放。

Imec的2nm forksheet具有42nm的接触栅极间距(CPP)和16nm的金属间距,均低于Nanosheet 45nm的接触栅极间距和30nm的金属间距。

Complementary FET(CFET)是另一种类型的GAA器件,由两个单独的纳米线FET(p型和n型)组成。一般pFET堆叠在nFET的顶部,消除了n-p分离的瓶颈,减少了电池有效面积。

去年11月,英特尔首席执行官Bob Swan曾提到,英特尔的3nm也将采用CFET。

但CFET及相关的晶体管也存在散热等挑战,还需要更多时间来开发,在各环节需要新的技术和设备。

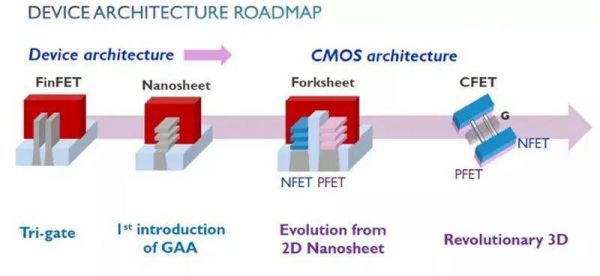

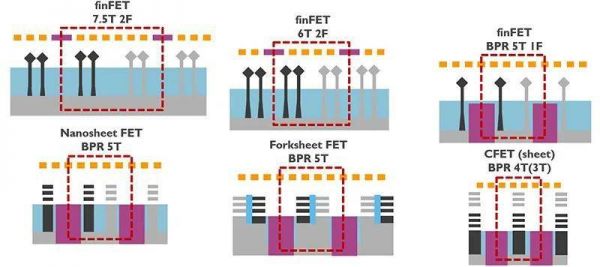

从FinFET到nanosheet再到forksheet和CFET

三、更精细的芯片“刻刀”:高数值孔径EUV

负责“雕刻”电路图案的核心制造设备是光刻机,它是芯片制造阶段最核心的设备之一,光刻机的精度决定了制程的精度。

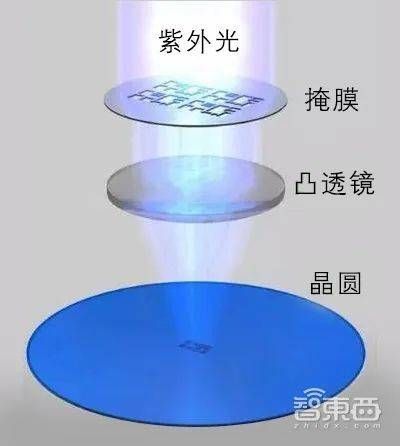

光刻机的运作原理是:先把设计好的芯片图案印在掩膜上,接着用激光光束穿过印着图案的掩膜和光学镜片,将芯片图案曝光在带有光刻胶涂层的硅片上。

此时,涂层被光照到之处发生反应溶解,没有被照到之处保持不变,掩膜上的图案就被转移到芯片光刻胶涂层上。

光刻原理简示

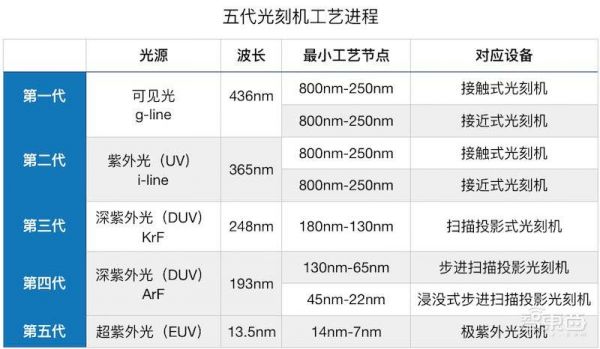

目前193nm浸没式光刻是应用最广且最成熟的技术,在22/16/14/10nm节点,主要芯片制造商均使用基于193nm浸没式光刻系统的双重成像(double patterning)技术。

到7nm及更先进的技术节点时,则需要波长更短的极紫外(EUV)光刻技术来实现更小的制程。而荷兰ASML是全球唯一有能力制造EUV光刻机的厂商。

面向3nm及更先进的工艺,芯片制造商或将需要一种称为高数值孔径EUV(high-NA EUV)的EUV光刻新技术。

Imec和ASML成立了联合研究实验室,专注于后3nm节点的纳米级元件制造蓝图,具体分为两个阶段:

第一阶段开发并加速EUV技术导入量产,第二阶段共同探索下一代high-NA EUV技术潜力,以制造出更小型的纳米级元件,推动3nm以后的半导体微缩制程。

根据ASML年报,他们正在研发的下一代极紫外光刻机将采用high-NA技术,有更高的数值孔径、分辨率和覆盖能力,较当前的EUV光刻机将提高70%。

值得一提的是,英特尔的3nm节点与ASML的High-NA EUV光刻机设备的量产时间相吻合,大约在2024年前后。

ASML 预测半导体制程升级规划

针对后3nm工艺,Imec重点投入的研发领域包括光阻技术、光罩的防尘薄膜技术、工艺优化。

一方面,更高的光阻剂往往会增加缺陷率,光阻技术还需进一步改进以降低缺陷率。

另一方面,透明度等方面的挑战致使EUV的光罩防尘薄膜发展相对缓慢。

幸运的是,现有的EUV掩模工具足以用于3nm及更高的工艺。

四、兼顾有机与无机材料:沉积和刻蚀从原子层到分子层

为了将微电子器件造的更小,芯片制造商必须把越来越多的电路塞进更小的薄膜和3D结构中,这对与半导体工艺兼容的沉积和刻蚀技术提出了更高的要求。

薄膜沉积是指在硅片衬底上生成特定功能薄膜层的工艺,所沉积的薄膜可以是导体、绝缘材料或半导体材料。

刻蚀机通过干刻蚀(用等离子体进行薄膜刻蚀)及湿蚀刻(液体腐蚀)的方法,根据印上去的图案刻蚀掉有图案(或没有图案)的部分,留下剩余的部分,芯片图案又从光刻胶涂层转移到了硅片上。

刻蚀原理简示

当今的芯片使用各种原子级加工工具生产。

原子层沉积(ALD)技术可将材料以单原子膜形式一层一层的镀在衬底表面,一次只能沉积一层。原子层刻蚀(ALE)技术是一种用于精密去除目标材料层的工艺。ALD和ALE均用于逻辑和存储器。

业界正在为3nm及更先进节点开发ALD和ALE的高级版本。

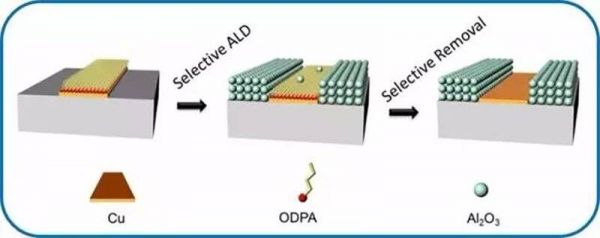

区域选择性沉积是一种先进的自对准图案化技术,将新颖的化学方法与ALD或分子层沉积(MLD)工具结合在一起,涉及在精确位置沉积材料和膜的过程,可减少流程中的光刻和刻蚀步骤。

从理论上讲,选择性沉积可用于在金属上沉积金属,在器件上的电介质上沉积电介质。不过目前区域选择性沉积仍存在一系列挑战,还在持续研发中。

ALD区域选择性沉积Al2O3原理图

对于在低纳米节点上开发的芯片,主要问题有器件的选择性增长、去除特定材料等。

因此,可以通过某种刻蚀去除出现在芯片中的异常现象,但晶圆上残留的任何材料都可能引起其他问题,例如掩膜堵塞。

业界一直在将嵌段共聚物视为生产这些紧密图案化表面的一种方式。嵌段共聚物将多种性质不同的聚合物链段连在一起,制备成一种特殊的线型聚合物,得到性能更为优越的功能聚合物材料。

过去,大部分商业努力都集中在无机材料上,无机材料比有机材料更致密、更薄。但随着越来越多的有机材料进入制造过程,仅适用于无机薄膜的ALD和ALE技术就不够用了。

分子层沉积(MLD)、分子层刻蚀(MLE)和ALD、ALE的方法类似,但和ALD和ALE不同的是,MLD和MLE也能用于产生和去除有机薄膜。

这种刻蚀技术可以选择性去除MLD层,而不会影响到附近的ALD层,为精确控制纳米级材料的几何形状打开了一扇新的大门。

先进制程设备布局

五、拒绝芯片瑕疵!卡住质量防线的检测

在芯片进入量产前,还需使用各种系统来查找芯片中的缺陷,也就是对芯片进行检测。

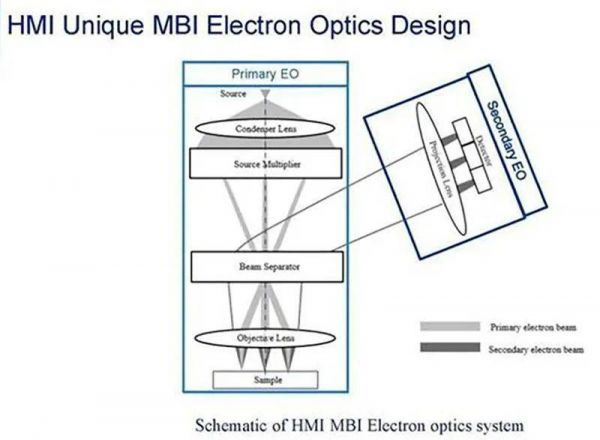

晶圆检测分为两类:光学和电子束。光学检查工具速度快,但分辨率受限;电子束检测工具分辨率更好,但速度偏慢。

因此,Applied Materials、KLA、ASML等公司均在开发多光束电子束检测系统,理论上来说,它能以较高的速度发现最困难的缺陷。ASML即开发了一种具有9条光束的电子束检测工具。

ASML多光束晶圆检测方法

不过芯片制造商希望使用具有更多光束的工具来加快检测过程。这项技术目前尚且面临不少挑战。

芯片制造商还使用各种量测系统来测量芯片内的结构。其中微距量测扫描式电子显微镜(CD-SEM)进行自上而下的量测,光学CD系统使用偏振光来表征结构。

十年前,许多人认为CD-SEM和OCD会走到尽头,因此加快了几种新型量测技术的开发,包括称为临界尺寸小角X射线散射(CD-SAXS)的X射线量测技术。

CD-SAXS是一种无损量测技术,使用小光束尺寸的可变角度透射散射来提供量测结果,X射线的波长小于0.1nm。其优点是能在于小波长能提供更高的分辨率,避免了OCD所具有的许多参数相关性问题,并且计算更加简单。

但在在某些情况下,X射线是由R&D设施中的大型同步加速器存储环产生的,这对晶圆厂来说很不切实际。

对于Fab工具,CD-SAXS需要紧凑的X射线源。三星,台积电等公司在实验室中均有CD-SAXS工具。

基于晶圆厂的CD-SAXS的问题在于X射线源有限且速度慢,会影响吞吐量。另外据VLSI研究公司总裁Risto Puhakka介绍,其成本也是一个问题,“可能贵5倍或10倍”。

Puhakka认为,短期内芯片制造商不会将CD-SAXS插入到在线监控流中。

CD-SAXS在内存方面正在取得进展。如今,在研发方面,内存制造商正在使用该技术来表征硬掩模和高宽比结构。在逻辑芯片方面,该技术仍处于概念阶段,X射线强度还将面临挑战。

六、像搭乐高一样堆叠封装芯片

传统设计方法是通过缩小每个节点上不同的芯片功能,并将它们封装到一个单片芯片上。

但是对很多人来说,集成电路的扩展变得愈发昂贵,且每个节点上的性能和功率优势都在减少,因此需要高级封装等替代方案。

当今高级封装技术能让内存更接近逻辑处理单元,提升互联密度和信号传输速率。

逻辑内核与存储单元之间的物理距离会导致延迟,人工智能等应用又需要密集的计算操作,信号从大型芯片的一端传输到另一端所花费的时间,远比使用高速接口从一个芯片传输到另一芯片所花费的时间更长。

因此,通过封装逻辑核心和内存,可以大大减低功耗并增加内存带宽。许多封装厂研发先进的封装技术,以增加晶体管速度,从而提高整个封装系统的性能。

在已量产的2.5D集成电路领域,台积电主推CoWoS工艺,英特尔主推EMIB工艺,三星主推FOPLP。

台积电先进封装技术一览

未来通过难度更高的硅通孔(TSV)3D封装技术,台积电将进一步量产系统整合SoIC、 WoW等3D集成电路,英特尔推出Foveros技术,三星推出3D SiC。

小芯片(chipset)是实现异构集成的一种新形式,通过在特定空间像乐高似的堆叠多种芯片,实现更快的开发速度和更高的计算力。

去年台积电展示的7nm小芯片系统就是一个很好的例子,通过采用COWOS封装技术和LIPINCON互连技术,将大型多核设计划分成多个小芯片,从而提供更高的良率和更好的经济性。

英特尔也做到将不同IP、不同工艺的各种方案封装在一起,从而省去漫长的重新设计、测试、流片过程。

2019年7月,英特尔推出将EMIB和FOVEROS相结合的CO-EMIB技术,无论是2D水平互连还是3D堆叠互连,单片与单片之间都可实现近乎于SoC级高度整合的低功耗、高带宽、高性能表现。

台积电、三星、英特尔均为堆叠封装技术的主要参与者

研究人员也在功率半导体封装方面进行改进。例如,碳化硅(SiC)比硅具有更高的击穿电场和热导率,供应商将SiC功率MOSFET和其他组件集成到功率模块中。

但要充分利用碳化硅,还需在封装方面做很多优化工作。Cree CTO John Palmour在最近的一次采访中表示,如果仅使用用于硅的标准功率模块设计,则只能获得碳化硅所应具有的性能的一半左右。

结语

随着半导体制程的不断发展,摩尔定律的推进节奏逐渐趋缓,延续摩尔定律的生命力需要创新技术和设备的突破。

胡正明教授曾说过,半导体行业大约每隔20年,就会有新的危机出现。20年前,大家一度非常悲观,看不清如何才能将芯片性能做得更好、功耗更低且控制住成本。

如今半导体行业回到了20年周期的“危机”循环节点,全球最顶尖的芯片公司都不知道,当先进制程走到5nm、3nm、2nm、1nm后,未来半导体行业的创新发展,路又在何方?

这个问题的答案,也许藏在人工智能、5G等新兴应用里,也许藏在半导体的新器件、新技术、新模式里,整个半导体行业都在不断探索前行。

无论未来谁是创新风暴的引领者,最终受益的都将是享用更高性能电子产品的每一个人。

参考来源:Imec,半导体工程

本文来自微信公众号:智东西(ID:zhidxcom),作者:心缘

网址: 芯片制程之战:三星台积电挺进3nm,英特尔们呢? http://www.xishuta.com/newsview22603.html

推荐科技快讯

- 1问界商标转让释放信号:赛力斯 95067

- 2人类唯一的出路:变成人工智能 20174

- 3报告:抖音海外版下载量突破1 19974

- 4移动办公如何高效?谷歌研究了 19396

- 5人类唯一的出路: 变成人工智 19282

- 62023年起,银行存取款迎来 10229

- 7网传比亚迪一员工泄露华为机密 8346

- 8五一来了,大数据杀熟又想来, 7727

- 9滴滴出行被投诉价格操纵,网约 7350

- 10顶风作案?金山WPS被指套娃 7158