「指甲盖」上集成500亿晶体管:全球首款2nm芯片制程发布,未来手机四天一充电?

编者按:本文来自微信公众号“新智元”(ID:AI_era),作者:新智元,编辑:小匀,36氪经授权发布。

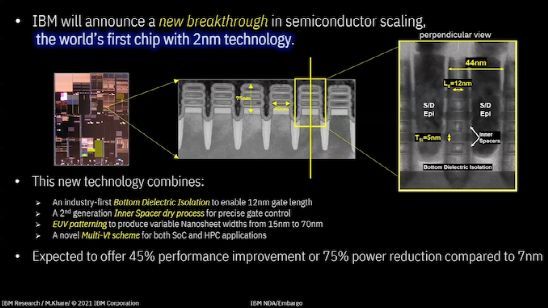

将500亿个晶体管集成到指甲大小的芯片上?蓝色巨人称:我们做到了!近日,IBM宣布了他们的2纳米工艺技术,并称比目前主流的7纳米芯片快 45%,功耗减少 75%。然而,2纳米的说法却引发了当下对工艺节点名称的新思考。

也许你都忘了,IBM曾是一家大牌的芯片制造商。

但它今天给我们提了个醒儿:全球第一个 2 纳米芯片制造技术,诞生在了纽约州奥尔巴尼的IBM研究院。

在IBM研究院的阿尔巴尼工厂制造的2纳米晶圆

每十年都是考验摩尔定律极限的期限,以2021为开端的十年也不例外。

随着极紫外(EUV)技术的到来,加上其他更多的技术改进,晶体管尺寸得以减少。但目前看来,这项技术已经趋于瓶颈。

据IBM称,其新推出技术这种架构可以平衡性能与能源效率——比目前主流的7纳米芯片快 45%,功耗减少 75%。

这个消息,就像一个重磅炸弹,在台积电、三星、英特尔盘踞太久的芯片行业,让IBM狠狠地刷了波存在感。

但必须澄清的是,虽然该工艺节点被称为「2纳米」,这个2nm跟传统谈论的线宽不一样。

全球首个2纳米芯片制造技术,但2纳米的标签你搞清了吗

在过去,这个尺寸曾经是芯片上二维特征尺寸的等效度量,如90纳米、65纳米和40纳米。

然而,随着FinFET和其他3D晶体管设计的出现,现在的工艺节点名称是对「等效2D晶体管」设计的解释。一般用晶体管密度可以更准确的衡量,如同英特尔倡导的那样。

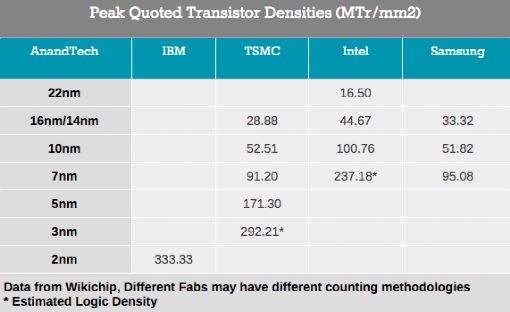

例如,英特尔的7纳米工艺将与台积电的5纳米工艺大致相同;台积电的5纳米工艺也甚至没有50%的改进(它比7纳米工艺只提供15%的改进),所以称其为5纳米工艺本身就有点牵强。根据IBM的说法,他们的「2纳米」技术比台积电的7纳米工艺有大约50%的改进,这样以来——即使按照当今最宽松的标准,也顶多是3.5纳米技术。

但这不代表IBM的新消息没有技术含量。

IBM表示,新芯片将在「手指甲大小」的芯片中配备多达500亿个晶体管,这使得IBM的晶体管密度为每平方毫米3.33亿个晶体管(MTr / mm 2)。

通过下表可以获得更好的比较:

不同的代工厂有不同的官方名称,有各种密度。值得注意的是,这些密度数字通常被列为峰值密度,用于晶体管库,其中芯片面积是峰值关注点,而不是频率扩展--由于功率和热方面的考虑,通常处理器最快的部分的密度是这些数字的一半

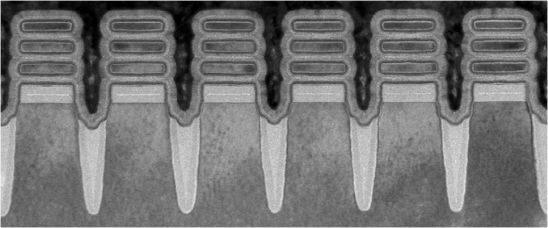

关于向全方位门/纳米片晶体管的发展,虽然IBM没有明确表示,但图片显示,这种新的2纳米处理器采用了三层GAA设计。

IBM 2纳米硅制造工艺的剖面图:叠加式GAA(Stacked GAA ,其中GAA是「切入环绕式栅极技术」的简称)

此前,三星在3纳米时引入GAA,而台积电则要等到2纳米。相比之下,英特尔将在其5纳米工艺中引入某种形式的GAA。

该工艺包括每个鳍片中的三个门-周围(GAA)纳米片通道。极端紫外线(EUV)处理对于定义工艺中的小尺寸是必要的,但它允许纳米片的宽度在15纳米到70纳米之间。为了呼应IBM早期在绝缘体上的硅(SOI)工作,该工艺包括一个底部电介质隔离,以实现12纳米的门长。IBM已经开发了一种内隔板干式工艺,以提供精确的栅极尺寸控制。该工艺支持多种阈值电压,用于SoC和高性能计算应用。这是首次在工艺的FEOL部分使用EUV图案,使关键层的设计的所有阶段都能使用EUV

据IBM称,这项先进技术的潜在好处可能包括:

手机电池寿命翻两番,只要求用户每四天给他们的设备充电一次。

减少数据中心的碳足迹,这些中心占全球能源使用量的1%,即5.8亿兆焦耳。将他们所有的服务器改为基于2纳米的处理器,有可能大大减少这一数字。

大大加快笔记本电脑的功能,从快速处理应用程序,到更容易地协助语言翻译,到更快的互联网访问。

有助于加快自动驾驶汽车等自主车辆的物体检测和反应时间。

另外,这项技术将使数据中心的电源效率、太空探索、人工智能、5G和6G以及量子计算等领域受益。

全球芯片巨头进程概览,IBM有可能挑战台积电地位吗?

好汉不复当年勇。蓝色巨人IBM早就没有芯片巨头这一形象了。

想当年美国存储器凭着Sematech联盟崛起,也是靠IBM慷慨捐赠的一条晶圆线。

的确,IBM现已将其大量芯片生产外包给三星电子。在纽约州奥尔巴尼(Albany)仍保留着一个芯片制造研究中心。该中心负责对芯片进行试运行,并与三星和英特尔签署了联合技术开发协议,以使用IBM的芯片制造技术。

纽约州Albany附近有很多比较出名的大学和研究中心:例如GE的全球研发中心、IBM、和相关的几家晶圆厂

也就是在这里,IBM闷声搞大事,加入了本属于台积电和三星的争夺战。

去年秋天,苹果的M1和A14与华为的麒麟9000一起到来,成为首批基于台积电5纳米技术节点工艺的处理器。

另一边,三星正在奋力追赶迟迟落后的五纳米制程。

其他制造商,如AMD和高通,现在通常使用台积电的7纳米芯片(尽管高通的骁龙 888是在三星的5纳米技术上制造的)。

而至于英特尔,这家芯片巨头计划在2025年和2027年分别完成3纳米和2纳米节点。在2023年之前该公司不太可能发布7纳米处理器——它目前正在使用10纳米和14纳米芯片。但是必须承认,英特尔的芯片在相同的纳米数字上往往比竞争对手有更大的晶体管密度。

与此同时,台积电也在研究2纳米工艺,其4纳米芯片工艺有望在2021年底实现风险生产,3纳米处理器预计将在2022年下半年推出,2纳米版本也于2019年开始研究,目前正在开发中。

但雄心归雄心,铠甲还是很重要的。

先进纳米制程所必须的极紫光刻机EUV,ASML在全球生产了100台,其中70台都归台积电。

IBM这项2纳米芯片制造技术,还需要几年时间才能推向市场。而届时台积电的3纳米或早已称新王了。

芯片上更多的晶体管也意味着处理器设计人员拥有更多的选择。IBM已经在最新一代的IBM硬件中实现了其他创新的核心级增强功能,例如IBM POWER10和IBM z15。

但更强大、更高效的CPU正奔赴而来,这不值得兴奋吗?

参考资料:

https://www.engadget.com/ibm-2nm-chip-power-efficiency-100001102.html

https://venturebeat.com/2021/05/06/ibm-details-planned-2-nanometer-chip-process/

https://www.anandtech.com/show/16656/ibm-creates-first-2nm-chip

相关推荐

「指甲盖」上集成500亿晶体管:全球首款2nm芯片制程发布,未来手机四天一充电?

芯片制程之战:三星台积电挺进3nm,英特尔们呢?

2nm芯片开启“明争暗斗”,日本野心不减

5nm制程即将上线,会是iPhone 12杀手锏吗?

2nm芯片开启“团战”模式

最前线丨3nm、5nm制程技术还没捂热,台积电又要开始研发2nm的芯片了

日本的2nm雄心

台积电迈向2nm,三星和英特尔慌了吗?

5G芯片之争:华为抢跑,削弱高通话语权

2nm开启“团战”模式

网址: 「指甲盖」上集成500亿晶体管:全球首款2nm芯片制程发布,未来手机四天一充电? http://www.xishuta.com/newsview42810.html

推荐科技快讯

- 1问界商标转让释放信号:赛力斯 95228

- 2人类唯一的出路:变成人工智能 21183

- 3报告:抖音海外版下载量突破1 21148

- 4移动办公如何高效?谷歌研究了 20339

- 5人类唯一的出路: 变成人工智 20338

- 62023年起,银行存取款迎来 10336

- 7五一来了,大数据杀熟又想来, 8596

- 8网传比亚迪一员工泄露华为机密 8505

- 9滴滴出行被投诉价格操纵,网约 8215

- 10顶风作案?金山WPS被指套娃 7230