一颗小小的芯片,为何会产生那么大的热

滚烫的手机,温度过高而死机的电脑,这些问题时常困扰着广大的使用者们,这背后的原因多半要归咎于芯片过热。实际上芯片的发热问题不仅造成了使用上的不便,也给生产者们带来了巨大的技术成本,并限制了芯片性能的进一步的提升。

一颗小小的芯片为何会产生那么大的热量?芯片的性能与发热量有什么关系?工程师和科学家们又是用什么方法来解决这一问题?本文就将为你揭晓以上问题的答案。

一 功耗是芯片的梦魇

1965年,英特尔创始人之一的戈登·摩尔提出了经典的摩尔定律, “每18个月性能提升一倍,价格降低一半”,这条金科玉律就像一座路标,指引着行业发展的方向与节奏。随之而来的就是更小的晶体管,频率更高的CPU,集成度更高的数字电路和更低的成本。一代又一代的芯片和电子产品由专用走向普及,并逐渐渗透到了生活和工作的方方面面。

也正是如此,人们打开了数字世界的大门,看到了前所未见的光景。但与此同时,芯片性能的跃升也逐渐遇到了瓶颈……

以栅极氧化层为例,在采用CMOS数字电路构造的CPU里,它起到关键的绝缘作用。栅极氧化层不仅要保证表面平整,不能有缺陷,为了符合半导体工艺标准,它的厚度也有一个理论的上限值。当制程工艺由90nm向65nm过渡时,虽然芯片的集成度得到了提升,但是想要将小于2nm的这层栅极氧化层的厚度继续降低,却是十分困难。这一技术难题让英特尔这样的芯片巨头也为之头疼。

随着芯片的加工工艺精度进入原子级别,任何缺陷都被会被无限放大,比如在内部结构中仅仅缺少一个原子的厚度,就可能引起非常大的漏电流,这样的漏电流不仅白白浪费了电能,更是引起芯片严重发热的原因。以早期的英特尔奔腾四CPU为例,有一半的功耗就是由于漏电被浪费了。

如今的CPU的单核速度可达到4GHz,算力的提升也带来了功耗和发热量的水涨船高,这时如果还照方抓药式地采用传统的风扇降温,CPU内部的热量就会迅速攀升甚至将其融化。为了兼顾算力和功耗,工程师则采用了双核芯片及多核的方法,走多核芯片路线以分担单颗CPU的工作负荷间从而降低功耗和发热。除此以外,此后材料的革新,也能够对功耗和散热起到了非常大的优化作用。

二 神秘的测试

测试是检验真理的唯一标准。就像学生时代的临考前,老师们千叮咛万嘱咐的一句话:做完题目别着急交卷,先检查检查,在半导体制造过程中更是如此,从芯片的制造到交付出货期间,芯片测试已成为了不可或缺的环节。

在所有电子元器件的制造工艺里面,存在着去伪存真的需要,为了实现试验的过程,就需要各种试验设备,这类设备就是所谓的ATE(Automatic Test Equipment)。

ATE是一种通过计算机控制,进行芯片、电路板和子系统等测试的设备,通过计算机编程取代人工劳动,自动化地完成测试序列。ATE的应用场合涵盖集成电路整个产业链,主要包括了芯片的设计验证、晶圆制造相关的测试到封装完成后的成品测试。

ATE市场的发展可以追溯到1960年代,早期的半导体测试设备发展并不完全是由独立的设备商引导,而是由半导体制造公司主导。仙童半导体(Fairchild)、德州仪器(TI)等制造企业生产ATE都是用于内部使用,而从1980年代起,ATE领域开始进行整合,2011年惠瑞捷(VERIGY)被收购后,形成了以泰瑞达(Teradyne)和爱德万测试的双寡头格局。

回顾ATE的发展史,可以说泰瑞达是“第一个吃螃蟹的人”。早在1960年,两位麻省理工高材生在波士顿创立了泰瑞达公司。如今,在波士顿总部的展示区域,依旧陈列着世界上第一台ATE设备D133,它是1961年推出的第一台二极管测试机,标志着自动测试设备迈入全新纪元。Teradyne(泰瑞达)的命名颇有意思,名字中的"Tera"取自10的12次方的前缀,"dyne"是力学的单位。如此命名,也意味着这家公司将是一股不容小觑的巨大力量。

从70年代到80年代早期的十年间,集成电路经历了由小规模到中规模再到大规模和超大规模的变迁。这时计算机控制的测试系统成为主要的测试设备。80年代中期,随着门阵列器件的成功开发,对于测试方面要求达到了256管脚,速度高于40MHz。进入到90年代,单片处理器单元(MPU)的问世也带来了高速高管脚数的ATE。随后多媒体器件的出现使ATE变得更加复杂,需要同时具有数字电路、模拟电路和存储器电路的测试能力。

近年来,工艺节点不断提升,芯片制程工艺不断逼近物理极限,这些也带来了更高的集成度。随之而来,整个芯片的功耗方案也要作出相对应的改变。

当下,先进制程芯片具有非常复杂的供电系统,测试成本不断增加的同时,测试环节对产品良率的监控将会愈发重要,这样的情况下,ATE该如何测试?

三 实际测试中的挑战

应用处理器的测试机里有两个非常重要的单元,其一是数字芯片测试的数字I/O,数字I/O承担了相对复杂的工作,可以抓取失效;另一个就是电源,虽然DC电源看起来比较简单,但在实际的大功率处理器的测试中,电源在起到非常重要的作用,因为它决定了测试质量,最终测试的良率也与电源的实际性能息息相关。

展开来看,应对不同的挑战,不同测试环节的测试参数和应用场景稍有区别,就需要采取不同的解决方案。

对于复杂的供电问题,利用模块化的供电策略可以降低多相位复杂供电的困扰。通过灵活地分配测试资源,将电源拆解成一个个小的电源模块,任意组合成小的单元模块给不同的电源轨供电,同时还可以利用冗余的电源模块来帮助已经预设好的模块降低供电电源轨的稳压压力。

简单举例,一个需要30安培的VDD引脚,如果每个通道支持5安培的输出能力,可以组合6个这样的单元来供电,同时利用冗余的通道组合单元与前面的6个单元组合在一起降低供电压力。

此外,还可以利用软件编程的方式设定上电次序、软启动等,以减少外围供电电路。

对于大多数应用处理器来说,工作频率与VDD一般呈现正相关性。在前期的设计验证中,厂商会尝试寻找sweet point使得芯片在有限的功耗下表现出更好的性能,在实际的生产测试中,可能会直接地设定一个指定的VDD,看其能否在这个特定的VDD下达到预期的频率。

数据整理来自泰瑞达

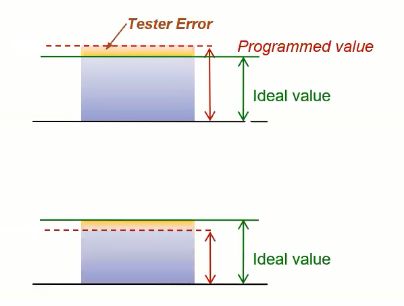

然而,在实际的测试中,没有一款测试机是完美的。实际操作中,芯片会经常性产生误差,一种方式是尝试编程稍高于芯片预设值的电压,由于考虑芯片的误差及所有的损耗,需要保证芯片引脚上的电压依然高于预期值。通过这种测试方法,即使仪表波动到最低的电压情况下,质量好的器件仍然可以pass,从而获得更高的良率。

另一种方式,直接将测试仪表的输出编程等于预期值,由于实际上一些测试机并不能达到良好的精准度,在一些情况下略低于输出,导致这部分的芯片实际测试电压低于预期值。

这两种方式会造成不同的负面效果。在第一种的情况下,VDD的预期值需要制定得更高一些,这样的话实际的电压会高于预期值,实际测试中的热损耗也会更大,在测试中就需要低速的向量帮助降温。

第二种情况下,虽然实际出货的产品都能够pass预期值,但是对于一些误差比较大的机器,会造成额外的良率损失。对于7nm、5nm的先进制程产品来说,良率是极其重要的一个因素,由于先进制程产品尤其是晶圆面积较大时的良率本身非常低,在此基础上如果又额外损失一部分良率,这对于器件制造成本是难以接受的。

面对种种挑战,我们该如何测试?测试机应该具备怎样的特性满足以上的诸多挑战需求呢?

四 不同测试挑战的对症下药

“Millivolts Matter”,每一个毫伏的精度都非常重要。越来越低的核心电压对电源的输出精度,以及动态响应提出了越来越高的要求。泰瑞达一直把电源仪表的输出电压能力作为仪表设计最重要的参数之一,这也是泰瑞达区分于众多ATE厂商的特征之一。

在实际测试过程中电源的供电不是完全平坦的,实际的电源功耗与实际工况有很大关系,甚至会导致芯片丢失状态,从而导致器件失效。这样的问题既难预测又很难排查。

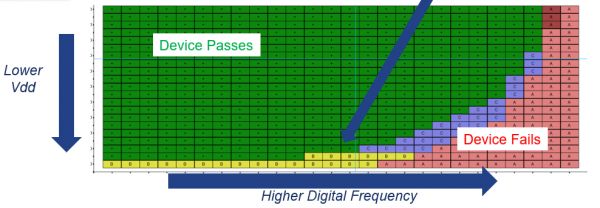

通过不断改变输出的VDD与Scan Shift频率来查看所有测试向量的输出结果,当VDD越低频率越高时,越容易发生失效。在实际的Shmoo测试案例中,泰瑞达的UltraFLEXplus具有更稳定的供电电源,这意味着可获得更高的边界良率,使得芯片更加贴近于真实的本征。这样一来,在实际产品中,我们对于芯片的实际工况便能够得到一个更加准确的推断,知道哪些情况是可以工作的,哪些情况是不能工作。总的来说,更好更稳定电源不仅能够提升良率,还能够认识芯片在真正工况下的工作状态。

数据整理来自泰瑞达

目前,很多芯片需要非常大的电流供电能力,输出一个非常大的电流能力对测试机来说已经不是一个难题了,很多测试机已经能够轻松供给1000A的输出能力。然而多工位测试的时候每个芯片的单个电源轨上电都要达到800 -1000A,测试机虽然能够满足1000A的静态供电,它是否能够满足0A到1000A的单步上电过程,成为了一个难题。在多工位测试的时候,泰瑞达所提供的解决方案就能够满足单步上电的大电源供给。

数据整理来自泰瑞达

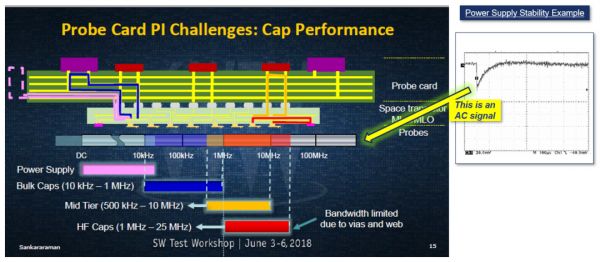

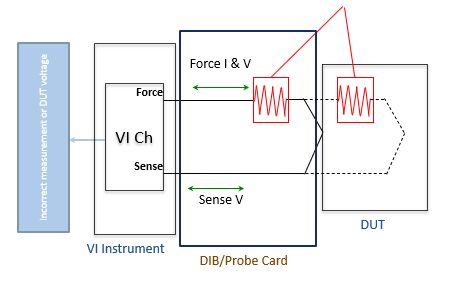

除了关注电源静态、动态的部分,在电源的外围电路设计上,socket、探针卡、loadboard等与电源的性能也是息息相关。

测试仪表的动态响应对直流电源的表现影响非常大,优秀的电源方案可以帮助减少外围电源电路的复杂度。传统的ATE解决方案首先需要板卡提供能量供给,大多供给从直流部分到100kHz的频域范围,针对低频、中频、高频等其他频段也需要增加不一样的外围电路,致使整体电路比较复杂。

泰瑞达侧重于简化电路设计,通过ATE本身就能提供从低频到中频的输出能力,不需要增加额外的外围电路,尽可能减少电容数量。在实际操作中,只需加入较少种类的低ESR/ESL陶瓷电容来帮助改变高频特性,令单个型号就可满足输出的动态性能。

这样的好处在于:1)降低电容值以加速恢复时间;2)电容少意味着充放电时间更快,也就意味着充放电的能量会变少,这样可以加速测试时间并降低socket被能量损伤的概率;3)降低电容使用种类,在使用单一电容的情况下,可以降低电路发生谐振、慢恢复等的可能性。

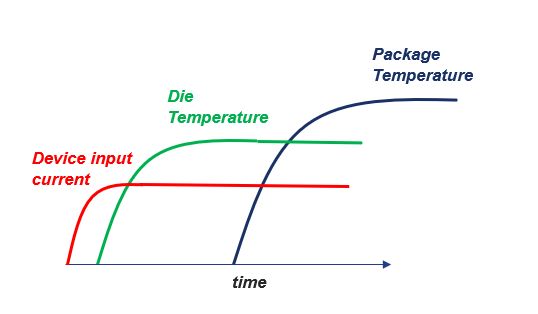

另一个比较大的挑战在于测试单元,大功率的先进制程芯片功率耗散非常大,多数输出的能量最终都会转化为热量。我们在测试时要避免芯片无限制地升温导致芯片“被烧坏”,而是希望在测试参数的时候做到可重复、可重现,使芯片维持在稳定的情况下测试,保证所有收取数据的一致性。最直接的办法可采用在测试单元的时候使用ATC(Automatic Temperature Control),常见的办法有三种:方案一)DUT Power Monitor;方案二)Die Temperature Monitor;方案三)Package Temperature Monitor。

数据整理来自泰瑞达

三种方式各有利弊,在时间上的效益也不同(如上图),泰瑞达更加倾向于使用方案一,其优点在于可以更早预判芯片接下来可能发生的状态并提前介入;其次,泰瑞达测试机原身也能够支持这种方式,输出每一个DPS当下负载的百分比以及输出电压的大小。

在很多实际量产的案例中,泰瑞达已经使用了这种监控方式,对比方案二、三可以更早预知芯片的实际工况。

芯片功率不断加大的情况下电路变得更加复杂,我们希望在测试的过程中所有的socket、探针卡、loadboard等都能得到比较好的监控,保证在短路、接触不良等异常情况发生时不会因此而损坏测试部件。

为避免这种情况发生,泰瑞达在设计大部分测试板卡的过程中会添加实时的报警机制,一旦任何异常发生,能够在不影响其他设备生产和中断生产的情况下,通过测试机作出实时警告,提前筛查避免异常情况的出现,减少测试漏测、质量事故等情况的发生。

数据整理来自泰瑞达

总结

半导体测试就是通过测量半导体的输出响应、预期输出、并进行比较以确定或评估集成电路功能和性能的过程,贯穿设计、制造、封装、应用全过程。随着半导体制造工艺要求的提升,测试环节在半导体制造过程中的地位随之不断提升。

半导体测试机的技术核心在于功能集成、精度与速度、降低成本与可扩展性。在泰瑞达看来,测试解决方案要有足够好的静态精度及稳压能力,同时在边界情况下获得更好的鲁棒性来帮助降低失效的概率;尽可能简化外围电路的设计,降低运营方面的损失,侧面降低测试成本;最后加入警报机制来提前预判,避免发生异常情况。

本文来自微信公众号 “半导体行业观察”(ID:icbank),作者:李寿鹏,36氪经授权发布。

相关推荐

一颗小小的芯片,为何会产生那么大的热

一颗小小的芯片,掩盖不住苹果的大野心

小小的光刻胶为何引发半导体行业震动?

汽车巨头何以被一颗小小的芯片卡住了脖子

芯片“热”了,芯片行业也变了

这一轮“芯片荒”是怎么产生的?

小小的 M1 芯片,也许决定了苹果的命运和未来

一颗芯片引发的投资狂潮

5nm芯片为何集体翻车?10年前困扰台积电三星的问题又回来了

因为一颗安全芯片,二手MacBook不好卖了

网址: 一颗小小的芯片,为何会产生那么大的热 http://www.xishuta.com/newsview50082.html

推荐科技快讯

- 1问界商标转让释放信号:赛力斯 95037

- 2人类唯一的出路:变成人工智能 19982

- 3报告:抖音海外版下载量突破1 19767

- 4移动办公如何高效?谷歌研究了 19209

- 5人类唯一的出路: 变成人工智 19079

- 62023年起,银行存取款迎来 10202

- 7网传比亚迪一员工泄露华为机密 8315

- 8五一来了,大数据杀熟又想来, 7549

- 9滴滴出行被投诉价格操纵,网约 7166

- 10顶风作案?金山WPS被指套娃 7146