400 层堆叠 3D NAND 闪存将至,东京电子宣布开发出全新蚀刻技术

来源: 时间:2023年06月12日 12:11

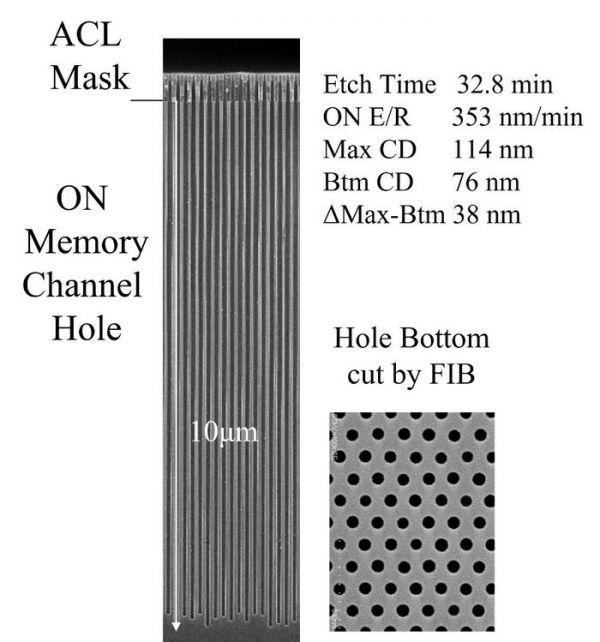

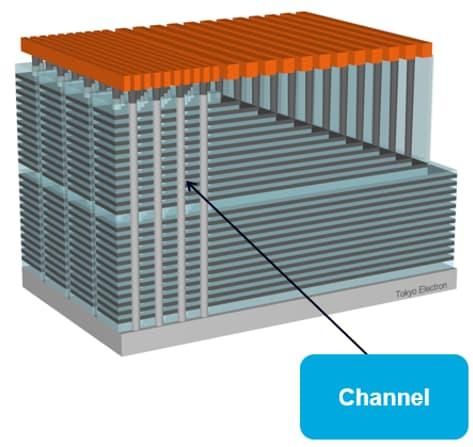

IT之家 6 月 12 日消息,东京电子(TEL)近日宣布,已开发出一种用于存储芯片的通孔蚀刻技术,可用于制造 400 层以上堆叠的 3D NAND 闪存芯片。TEL 表示,该技术首次将电蚀刻应用带入到低温范围中,并创造性地发明了具有极高蚀刻速率的系统。

▲ 图源 东京电子

▲ 图源 东京电子具体而言,这项新技术可以在短短 33 分钟内完成 10 微米深度的高纵横比(IT之家备注:纵横比是指晶圆上形成图案的深度与宽度之比)蚀刻,与此前的技术相比耗时大幅缩短。TEL 介绍,该技术的应用不仅有助于制造更高容量的 3D NAND,还能够将生产工艺中给全球变暖造成的风险减少 84%。

▲ 图源 东京电子

▲ 图源 东京电子TEL 预告,研发团队将于 6 月 11 日-16 日在日本京都举行的 2023 年超大规模集成电路技术和工艺研讨会上发布最新成果和报告。

发布于:山东

相关推荐

英特尔发布144层3D NAND闪存,未来固态盘总成本将低于传统硬盘

焦点分析 | 为什么英特尔要出售NAND闪存业务?

芯片,全面走向3D

SK海力士宣布量产238层NAND Flash!

6月9日:4D NAND闪存开始量产,这种半导体设备需求大增受益

韩国芯片,想再赢一次

NOR Flash,也要走向3D?

“3D堆叠”推动半导体继续进化

存储芯片“寒冬”下,韩国芯片大厂仍在进攻

昂贵的复仇背后:中日韩的存储战争

网址: 400 层堆叠 3D NAND 闪存将至,东京电子宣布开发出全新蚀刻技术 http://www.xishuta.com/newsview78430.html

推荐科技快讯

- 1问界商标转让释放信号:赛力斯 95228

- 2人类唯一的出路:变成人工智能 21183

- 3报告:抖音海外版下载量突破1 21148

- 4移动办公如何高效?谷歌研究了 20339

- 5人类唯一的出路: 变成人工智 20338

- 62023年起,银行存取款迎来 10336

- 7五一来了,大数据杀熟又想来, 8596

- 8网传比亚迪一员工泄露华为机密 8505

- 9滴滴出行被投诉价格操纵,网约 8215

- 10顶风作案?金山WPS被指套娃 7230

科技快讯热点排名

科技快讯热点