韩国存储双雄,再次领先

本文来自微信公众号:半导体行业观察 (ID:icbank),作者:李晨光,题图来自:视觉中国

在经历了前两年的芯片短缺之后,半导体市场进入了长期的下行周期。

其中,存储市场无疑是最惨的。过去几个季度,存储市场经历了过去15年来最严重的低迷。自2021年第三季度以来,DRAM和NAND芯片价格分别下降了57%和55%。

与之相对应的,存储芯片厂商无一不在饱经风霜,存储芯片巨头的季度营收基本跌去了一半。2022年半导体销售额ToP5企业中,有三星电子、SK海力士、美光3家存储芯片厂商。然而,从Omdia近日披露的数据来看,2023年第1季度ToP10榜单中仅剩下三星一家存储厂商。而上一次SK海力士和美光未能跻身前十还是在2008年。

种种迹象都反映出存储市场正在经历“寒冬”。为了控制市场波动、降低库存挤压,SK海力士、三星电子、美光科技等存储芯片大厂纷纷释出降价、减产策略。

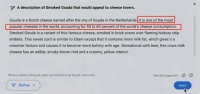

尽管当前存储市场遭受重创,但长期来看依旧潜力巨大。根据Yole数据预计,2025年存储芯片收入将增长至超过2000亿美元的新纪录高位。

面对市场周期的波动,尽管存储芯片大厂在缩减资本开支,降低产能,但围绕技术创新和产品布局的步伐从未止步。尤其是韩国存储双雄三星电子和SK海力士,双方的竞争态势已日趋白热化。

力争DRAM、NAND基本盘

从存储芯片类别看,DRAM约占存储器市场53%,NAND Flash约占45%,二者份额合计达98%,为存储器市场的两大标杆产品,也是三星电子和SK海力士展开竞争的“基本盘”。

DRAM:发力先进制程

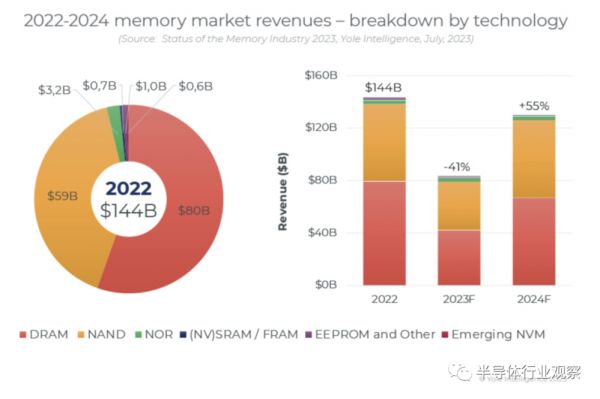

面对DRAM市场的萧条,行业厂商正在持续研发推出1α、1β、1γ或更先进制程的DRAM产品,尝试以技术创新在逆境中站稳脚跟。

不难理解,对DRAM芯片而言,先进制程意味着高能效与高容量,以及更好的终端使用体验。

从存储巨头的工艺制程发展历程来看,在2016-2017年进入1X(16nm-19nm)阶段,2018-2019年为1Y(14nm-16nm),2020年处于1Z(12nm-14nm)时代,目前继续向10nm逼近,最新的1α节点仍处于10+nm阶段。后续,行业厂商继续朝着1β、1γ或更先进技术阶段继续迈进。

2022年10月,三星公布的技术路线图显示,预计2023年三星将进入1βnm工艺阶段,即第五代10nm级别DRAM产品(另有消息称,三星将考虑跳过1β DRAM,直接研发1γ DRAM);同年12月,三星开发出首款采用12nm级工艺技术打造的16Gb DDR5 DRAM,与上一代产品相比,最新的12nm级DDR5 DRAM功耗降低了23%,晶圆生产率提高了20%。今年5月该产品已开始量产。

据了解,结合先进的多层EUV光刻技术,这款产品拥有三星最高的DDR5 Die密度,可使晶圆生产率提高20%,功耗有望节省约23%,最高支持7.2Gbps的运行速度。为了抢占逐渐扩大的DDR5市场,三星计划从2023年开始批量生产,并向数据中心和人工智能等领域客户供货。

而SK海力士重点发力存储产品的运行速度。今年5月,SK 海力士宣布已经完成了1β制程技术(第五代10nm等级) 研发,并将其技术生产的DDR5 服务器DRAM 进行英特尔数据中心存储器认证程序。

据介绍,SK海力士这次提供的DDR5 DRAM产品运行速度为6.4Gbps,也是同类产品里速率最高的,与初期的测试品项相比,数据处理速度提高了33%。而且,其采用了HKMG(High-K Metal Gate)制程技术,相较第四代10nm等级的1α制程技术的产品,功耗降低了20%。

SK海力士希望2023年开始量产最先进的1β制程技术产品,以业界最高DRAM竞争力水准改善2023 年下半年的业绩。此外,SK海力士还打算1β制程技术延伸到LPDDR5T、HBM3E 等产品上。

三星、SK海力士等DRAM厂商争相爆出有关第五代1β DRAM的最新研发进展,新一代产品在数据处理速度、功耗、耗电量等方面都有了显著提升,在移动设备、智能车辆、数据中心以及人工智能等领域的应用将更加广泛。

与此同时,存储厂商又开始了对下一代工艺节点1γ DRAM的研发。

业界认为1γ工艺是DRAM接下来的竞争关键。赛迪顾问集成电路高级分析师杨俊刚表示,1β DRAM产品主要受存储市场萎靡影响,市场空间相对有限。预计存储市场在2023年底或2024年上半年开始反弹,按照DRAM市场技术迭代速度,市场复苏刚好迎来1γ DRAM产品推出时间,所以1γ DRAM产品成为市场复苏后各家竞争关键。

三星近期放出的消息也侧面印证了这一观点。三星为了扩大与竞争对手的技术差距,已经要求其研究人员停止或跳过1β DRAM的开发,新的目标是在今年6月前完成11纳米的第六代1γ DRAM的开发。

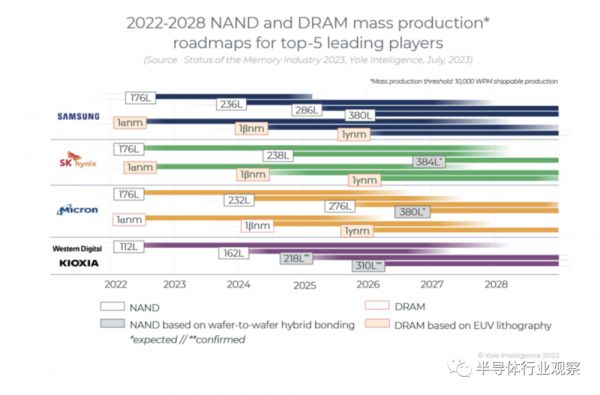

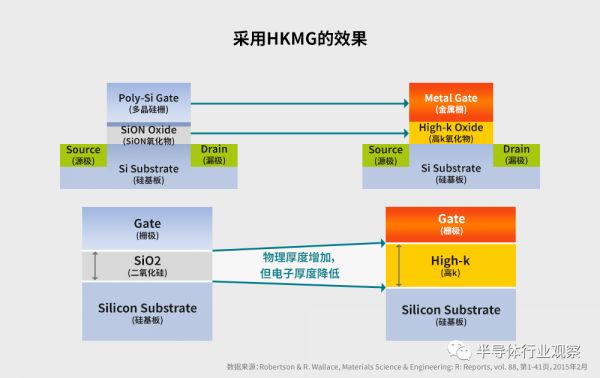

3D DRAM 是一种采用全新结构的存储芯片。简单来说,现有DRAM产品开发的重点是通过晶体管微缩来提高密度,但随着线宽进入10nm范围,业界开始面临电容器漏电和干扰等物理限制。为此,三星、SK海力士等一直在开发图案化、材料和架构方面的颠覆性解决方案,HKMG(High-k/Metal Gate)则成为突破这一困局的解决方案。

Transistor Scaling(晶体管微缩)

另一方面,3D DRAM顺势成为了存储厂商迫切想突破DRAM工艺更高极限的新路径。

三星电子和SK海力士等全球DRAM巨头正在加速推进3D DRAM的商用化。三星和SK海力士的高管在官方活动上曾表示,都将3D DRAM作为克服DRAM物理极限的一种方式。三星表示,3D DRAM是半导体行业未来的增长动力;SK海力士则认为,大概在明年,关于3D DRAM的电气特性细节将被公开,从而决定其发展方向。

NAND:芯片堆叠层数之争

NAND闪存芯片是最主要的存储芯片,可以实现大容量存储、高写入和擦除速度,多应用于大容量数据存储,例如智能手机、平板电脑、U盘、固态硬盘等领域。

2007年,随着2D NAND达到规模极限,东芝率先提出了3D NAND结构概念。2013年三星则率先推出了“V-NAND”,也就是3D NAND。其中的V代表Vertical,垂直的意思,这是一种通过垂直堆叠3D空间中的穿孔连接其单元层的解决方案,这种3D设计方式不仅带来了技术性能的提升,而且还进一步控制了成本。

三星率先将3D NAND闪存从技术概念推向了商业市场。

随后,V-NAND闪存不断发展,每一代新的V-NAND都带来了显着的性能提升,以及更低的功耗。2013年三星开发的第一个V-NAND闪存仅有24层,目前三星的V-NAND已经发展到了第8代的236层。

去年11月,三星宣布已开始量产三星产品中具有最高存储密度的1Tb三级单元(TLC)第8代V-NAND,其I/O速度高达2.4 Gbps,相比上一代提升了1.2倍,这可以满足PCIe 4.0和更高版本PCIe 5.0的性能要求。三星第8代V-NAND层数达到了236层。

2023年初,三星还制定了开发新一代3D NAND的计划:2024年推出的第九代3D NAND有望达到280层;第十代3D NAND有望跳过300层的区间,达到430层,预计将于2025-2026年推出。此外,三星还计划到2030年推出超过1000层的产品,以更好地支持未来的数据密集型技术。

三星虽是NAND闪存技术的奠基者并在过去一直领导市场发展,但在200层以上的竞争上,SK海力士也表现不俗。

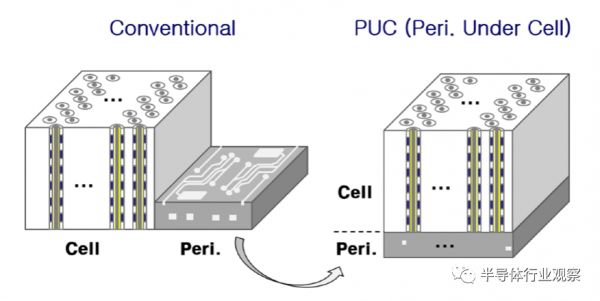

2018年11月,从第四代96层3D NAND开始,SK海力士推出了新的命名法——4D PUC(Periphery Under Cell),PUC是一种将外围电路重新定位到电池底部的技术,如下图所示。

相比3D方式,4D架构具有单元面积更小,生产效率更高的优点。为成功研发4D架构的芯片,SK海力士采用了电荷捕获型技术(CTF)和PUC技术,进而确保了成本、性能、产品质量等层面的全球领先竞争力。

4D NAND(图源:SK海力士)

98层之后,SK海力士陆续开发出128层、176层3D NAND。2022年8月,SK海力士宣布开发出最新的238层4D NAND闪存,并已于今年6月开始投入量产。(4D NAND代表的是一种先进性,而不是指进入第四维度)

据介绍,SK海力士的238层NAND闪存成功堆栈更高层数的同时,实现了业界最小的面积,生产效率比上一代的176层提升了34%。此产品的数据传输速度为每秒2.4Gb,号称比上一代的速度快50%,并且改善了约20%的读写性能。

在ISSCC 2023会议期间,SK海力士公布了在3D NAND闪存开发方面的最新突破,展示了其最新300层堆叠第8代3D NAND Flash的原型。

据SK海力士介绍,第8代3D NAND闪存主要运用了五个方面的技术,包括引入三重验编程(TPGM)功能,可缩小电池阈值电压分布,将tPROG减少10%,从而提高性能;自适应未选字符串预充电(AUSP),另一种将tPROG降低约2%的方法;编程虚拟串(PDS)技术,降低通道电容负载来缩短tPROG和tR的世界线建立时间;平面级读取重试(PLRR)功能,允许在不终止其他平面的情况下改变平面的读取级别,从而立即发出后续读取命令,最终提高了服务质量和读取性能。

SK海力士没有提供第8代3D NAND闪存的时间表,有行业人士估计,可能要等到2024年末或2025年某个时候才会上市。与此同时,SK海力士的第7代238层3D NAND闪存预计将被整合到2023年推出的新款闪存产品的生产周期里。

早在2019年,SK海力士就做出过大胆假设,计划2025年推出500层堆叠产品,并在2032年实现800层以上。

自从NAND闪存进入3D时代,芯片的层数比拼一直是各大NAND闪存芯片厂商竞争的重点,堆栈层数犹如摩天大楼一样越来越高。在3D NAND技术赛跑中,存储厂商从最初的24层、32层,一路堆到了128层、176层,直至200+层。层数越高,NAND闪存可具有的容量就越大,增加层数以及提高产量也是衡量技术实力的标准。

纵观当前全球的闪存格局,层数之争依旧是NAND闪存的主旋律。各大厂商纷纷采取措施,为尽可能多地占领市场的进行扩产,正在往更多层数进行技术迈进。

虽然现在还无法预测3D NAND最高可堆叠至多少层,不过随着头部企业持续加大3D NAND闪存市场布局,推动技术创新和演进,3D NAND闪存堆栈高度不断突破极限。

但需要强调的是,虽然3D NAND未来发展方向是堆栈添加更多的层,但NAND层数的竞争将对制造工艺带来更大挑战。正如三星高管所言,为了推动1000层的NAND技术,将面临稳定性问题,就像建造摩天大厦一样必须考虑坍塌、弯曲和开裂等因素。此外,他们还必须解决连接孔加工工艺、电池干扰最小化、层高缩短以及每层储存容量扩大等问题。

“基本盘”之外,竞争再现新高地

除了在DRAM和NAND上的比拼之外,韩国存储双雄在GDDR、LPDDR、HBM、PIM、UFS等细分赛道仍展现出新的竞争姿态。

GDDR:GDDR7,释放下一代显存潜力

GDDR(Graphics DDR),即图形DDR,它是为了设计高端显卡而特别设计的高性能DDR存储器规格,是打破“内存墙”的有效方案。

去年,三星公布了为GPU和服务器开发GDDR7 DRAM的计划。近日,三星宣布已完成 GDDR7 DRAM芯片的开发,将有助于提升在需要出色图形性能的领域的用户体验,例如工作站、个人电脑和游戏机,并有望扩展到未来的应用领域,如人工智能、高性能计算(HPC)和汽车车辆等。

据了解,三星的GDDR7 DRAM拥有破纪录的1.5TBps带宽,比GDDR6 DRAM高出40%,能效也比GDDR6 DRAM芯片高出20%。得益于PAM3(脉冲幅度调制)信号方法的增强,它的每引脚速度为32Gbps,比上一代产品高出33%。

三星还为其新芯片提供了较低电压的选择,为了减少热量产生,除了IC架构优化之外,三星还在封装中使用了具有高导热性的新型EMC材料。所有这些改进使其热阻降低了70%,从而提供了更稳定的产品,即使在高压力的操作条件下也能表现良好。

三星的重要客户将于今年开始测试GDDR7 DRAM芯片进行验证。但由于没有来自JEDEC的硬性承诺,因此没有预计GDDR7发布的具体时间表。鉴于如今有如此多的AI和HPC公司致力于带宽需求高的产品,其中一两家可能会更快发布依赖GDDR7显存的解决方案。但GDDR7的大规模采用预计会与AMD和NVIDIA的下一代图形卡的量产同时发生。

反观SK海力士,其近年来在GDDR闪存颗粒上的信息披露并不多,而是更多在强调以基于GDDR为接口的DRAM存内计算产品GDDR6-AiM(PIM)及其优势,此部分放在下文做详细介绍。

HKMG技术赋能LPDDR

LPDDR指的是Low Power DDR,中文全称为低功耗双信道同步动态随机存取内存,通常以先进封装技术直接堆在CPU处理器上方,减少通道宽度以及其他一些牺牲部分反应时间的方法来降低体积和功耗。因此,是移动应用场景的主流内存产品。

2022年10月,SK海力士宣布开始销售基于HKMG技术的全新1αnm LPDDR5X DRAM, 即便在低功率设置下也实现了晶体管性能的显著提高。

SK海力士官宣LPDDR5X LPDDR开始销售

SK海力士的LPDDR5X DRAM是首款在低功耗应用中使用HKMG成功批量生产的产品,通过大尺度微缩,同时利用全新HKMG晶体管构建块的优势,晶体管的性能获得显著提升;考虑到HKMG的固有特性和针对HKMG优化的设计方案,可以有效控制泄漏电流,较之上一代产品速度提高33%,功耗降低25%。SK海力士的技术不仅达到行业的目标标准,还因为最低功耗而实现ESG价值最大化。

采用HKMG的效果

借助HKMG,一层薄薄的高k薄膜可取代晶体管栅极中现有的SiON栅氧化层,以防止泄漏电流和可靠性降低。此外,通过减小厚度,可以实现持续微缩,从而显著减少泄漏,并改善基于多晶硅/SiON的晶体管的速度特性。

在SK海力士推出LPDDR5X后不久,三星电子也紧接着宣布称,其最新与移动处理器大厂高通合作的LPDDR5X DRAM,日前以8.5Gbps的业界最快速度通过了验证。

三星电子存储产品规划团队执行副总裁Daniel Lee表示,8.5Gbps LPDDR5X DRAM的联合验证,使我们能够将这一高速存储介质的市场推广速度加快一年多,这是我们与高通技术公司长期合作取得的巨大成就。

随着LPDDR内存的使用范围不断扩大到智能手机以外的人工智能和数据中心应用,存储和SoC供应商之间的紧密合作变得更加重要。SK海力士和三星将继续积极与行业创新者合作,以提高生态系统对未来LPDDR标准的准备程度。

存储双雄竞逐HBM

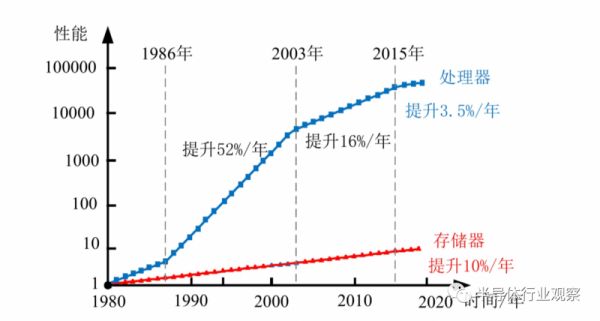

众所周知,由于处理器与存储器的工艺、封装和需求的不同,二者之间的性能差距越来越大。

存储器数据访问速度跟不上处理器的数据处理速度,数据传输就像处在一个巨大的漏斗之中,不管处理器灌进去多少,存储器都只能“细水长流”。有数据显示,处理器和存储器的速度失配以每年50%的速率增加。

两者之间数据交换通路窄以及由此引发的高能耗两大难题,在存储与运算之间筑起了一道“内存墙”。与此同时,随着数据的爆炸式增长,内存墙对于计算速度的影响愈发显现。

CPU与存储器发展趋势

为此,业界希望通过增加存储器带宽解决大数据时代下的“内存墙”问题,HBM便应运而生。

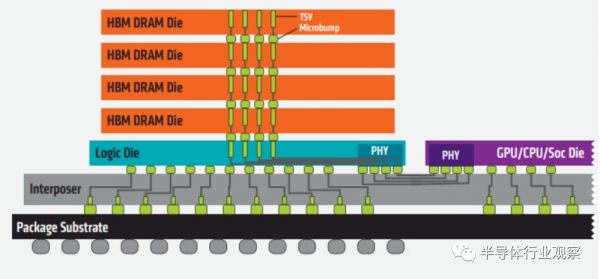

HBM(High Bandwidth Memory,高带宽内存)是一款新型的内存芯片,其实就是将很多个DDR芯片堆叠在一起后和GPU封装在一起,实现大容量、高位宽的DDR组合阵列,该技术可以说是DRAM从传统2D向立体3D发展的主要代表产品,开启了DRAM 3D化道路。

HBM主要是通过硅通孔(TSV)技术进行芯片堆叠,以增加吞吐量并克服单一封装内带宽的限制,将数个DRAM裸片垂直堆叠,裸片之间用TVS技术连接。从技术角度看,HBM充分利用空间、缩小面积,正契合半导体行业小型化、集成化的发展趋势,并且突破了内存容量与带宽瓶颈,被视为新一代DRAM解决方案。

裸片之间用TSV技术连接

在内存领域,三星和SK海力士围绕关于HBM的竞赛已悄然打响。

自2014年首款硅通孔HBM产品问世至今,HBM技术已经发展至第四代,分别是:HBM、HBM2、HBM2E、HBM3,HBM芯片容量从1GB升级至24GB,带宽从128GB/s提升至819GB/s,数据传输速率也从1Gbps提高至6.4Gbps。

HBM性能演进(图源:Rambus)

与传统DRAM相比,HBM具备高带宽、高容量、低延时与低功耗等优势,可以加快AI数据处理速度,更适用于ChatGPT等高性能计算场景。据了解,在英伟达A100/H100等高端GPU中,HBM的渗透率接近100%。

SK海力士是HBM市场的先行者,也是全面布局四代HBM的厂商。2014年,SK海力士与AMD联合开发第一代硅通孔HBM产品;2018年SK海力士发布第二代HBM产品HBM2;随后2020年SK海力士发布第三代HBM——HBM2E,作为HBM2的扩展版本,性能与容量进一步提升;2021年10月SK海力士成功开发出第四代产品HBM3,并于2022年6月开始量产。

SK海力士今年4月20日宣布,在全球首次实现垂直堆叠12个单品DRAM芯片,成功开发出最高容量24GB的HBM3 DRAM。该产品容量较上一代HBM3 DRAM提升50%。SK海力士已向客户提供样品,正接受客户公司的性能验证。

在AI市场夺得先机,是SK海力士如此迫切地推陈出新的主要原因。值得注意的是,英伟达为SK海力士HBM产品的大客户,英伟达已将16GB HBM3 DRAM搭配A100 GPU供ChatGPT使用,并已将SK海力士的第四代HBM安装至性能更强的H100 GPU上。SK海力士也按照英伟达的计划,在去年增加了HBM3 DRAM的产量。

另外,值得关注的是,MR-MUF是SK海力士首先开发的技术,据了解目前只有SK海力士使用该技术生产HBM。

SK海力士在近期的投资者活动日中强调,他们已开发出不同于竞争对手的封装技术(MR-MUF)并以长期独家的方式从合作伙伴那里获得关键材料,以此保障了其技术优势。

MR-MUF封装是当半导体芯片附着到电路上并且芯片向上堆叠时,用一种称为环氧膜塑料(EMC)的材料填充并附着芯片之间的空间的工艺。之前的竞争对手在此过程中使用了非导电膜(NCF)技术。MR-MUF封装对HBM芯片的外部结构有重大影响。SK 海力士在创建12层HBM3时,将一款产品中堆叠的DRAM数量从8个(16GB)增加到12个,从而将容量增加了约50%。

凭借这项技术,SK海力士实现了24GB的最大当前容量。SK海力士认为,MR-MUF封装技术将有效保持其计划于明年发布的第五代HBM3E的市场竞争力,超越目前已量产的第四代产品HBM3。

随着HBM3E需求的爆炸性增长,产量显着增加。SK海力士决定使用最新的尖端10纳米级第五代 (1β) 技术大幅提高明年的产量。大部分增量将由HBM3E填充。这表明SK海力士正在以HBM为首要业务战略,全力克服半导体低迷。据悉,SK海力士约40%的营业利润来自HBM。

三星也在积极跟进,三星对HBM的布局从HBM2开始,目前,三星已经向客户提供了HBM2和HBM2E产品。2016年三星量产HBM2;2020年三星推出了HBM2。

在2022年技术发布会上发布的内存技术发展路线图中,三星展示了涵盖不同领域的内存接口演进的速度。三星HBM3技术2022年已经量产,其单芯片接口宽度可达1024bit,接口传输速率可达6.4Gbps,相比上一代提升1.8倍,从而实现单芯片接口带宽819GB/s

另据媒体报道,三星已于今年4月26日向韩国专利信息搜索服务提交“Snowbolt”商标申请,预估该商标将于今年下半年应用于DRAM HBM3P产品。

预计三星HBM3P接口速度将高达7.2Gbps,数据传输率相比这一代提升10%,从而将堆叠的总带宽提升到5TB/s以上。HBM3P单芯片和堆叠芯片都将实现更多的总带宽提升,而这也将会成为人工智能应用的重要推动力,预计在2025年之后的新一代云端旗舰GPU中看到HBM3P的使用,从而进一步加强云端人工智能的算力。

集邦咨询数据显示,2022年三大原厂HBM市占率分别为SK海力士50%、三星约40%、美光约10%。

对于市场份额占比情况,三星电子负责半导体业务的DS部门总裁 Kyung Kye-hyun在7月份的员工内部沟通活动上表示,“三星HBM产品的市场份额仍超过50%”,他驳斥了有关该公司内存竞争力正在下降的担忧。

无论怎样,随着高性能存储半导体市场有望快速增长,HBM相关市场预计每年增长40%以上,三星电子和SK海力士之间的HBM产品开发竞争仍在升温。

PIM,打破芯片“内存墙”

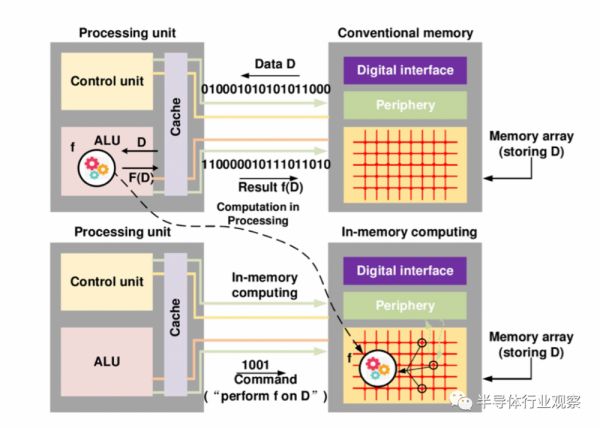

如果是HBM是通过增加存储器带宽来解决大数据时代下的“内存墙”问题,那么,存算一体(PIM)就是另一种解决“存储墙”与“功耗墙”问题的技术路径。

存算一体,又称存内计算,是一项打破传统冯诺依曼架构的新型运算架构,通过将存储和计算有机结合,直接利用存储单元进行计算,极大地消除了数据搬移带来的开销,解决了传统芯片在运行人工智能算法上的“存储墙”与“功耗墙”问题,可以数十倍甚至百倍地提高人工智能运算效率,降低成本。

存算一体概念图

随着AI的发展数据量暴增,存储墙、功耗墙成为越来越不容忽视的问题,存内计算已然成为新趋势。

对此,SK海力士开发出了公司首款基于PIM技术的产品——GDDR6-AiM(Accelerator-in-Memory,内存加速器)的样本。GDDR6-AiM是将计算功能添加到数据传输速度为16Gbps的GDDR6内存的产品。与传统DRAM相比,将GDDR6-AiM与CPU、GPU相结合的系统可在特定计算环境中将演算速度提高至最高16倍。

此外,GDDR6-AiM的工作电压为1.25V,低于GDDR6内存的标准工作电压(1.35V)。不仅如此,PIM的应用还减少了与CPU、GPU的数据传输往来,从而降低了CPU及GPU的能源消耗,借此GDDR6-AiM成功使功耗降低80%。GDDR6-AiM有望在机器学习、高性能计算、大数据计算和存储等领域有广泛应用。

SK海力士AiM的另一大优势在于他们已经实现了全套软件栈,包括设备驱动、runtime库、框架和应用等,也支持AiM软件仿真器,支持用户自行开发AI应用,而无需硬件评估板。

其实三星在PIM上也早有布局,早在2021年初推出HBM2E后,三星就已经开始规划如何充分利用这些高带宽内存的性能,其中之一就是PIM。

与SK海力士不同的是,三星打造的首个PIM为HBM-PIM,在内存核心中集成了名为可编程计算单元的AI引擎,用于处理一部分的逻辑功能。经过测试,HBM-PIM可推升2.5倍系统效能,且降低逾60%的能耗。

三星表示,HBM-PIM测试结果展现出庞大的商业潜力,随着技术发展标准化,技术应用将进一步扩大范围,并延伸至新世代电脑,AI应用HBM3、智能终端移动存储及数据中心存储模组。

除了这种将PIM集成到商用AI加速器的方案以外,三星也同时推出了直接将PIM集成到DRAM模块中的方案AXDIMM,通过直接在DRAM模块中对多组内存芯片进行并行运算,减少了CPU和DRAM之间的大量数据移动。

此外,三星还在研究基于MRAM的PIM技术,众所周知,MRAM比DRAM的速度更快,而且运行时更省电。三星在2022年1月12日在顶级期刊nature发表了题为“crossbar array of magnetoresistive memory devices for in-memory computin”的论文,实现了在MRAM上的存内计算

从三星半导体的PIM技术展示来看,他们也计划将这一技术应用到GDDR和LPDDR中,不过这几年间的主要技术公开展示都集中在HBM-PIM上。

写在最后

尽管半导体产业发展暂时进入“寒冬”,但从韩国存储双雄的动态和布局来看,存储赛道上的技术竞争仍旧十分激烈。

无论是第五代10nm级DRAM技术,还是更高层数堆叠的NAND Flash,以及HBM、PIM等创新技术,存储大厂都在积极发力,以保持市场领先地位,并满足市场对高容量、高性能产品需求,呈现出持续发展的潜能。

与此同时,在复杂的国际贸易关系背景下,三星电子和SK海力士这两家韩国存储巨头,或许还将填补美光被禁后出现的市场空缺,进一步吃到市场红利,逐渐拉开与竞争对手的身位。

本文来自微信公众号:半导体行业观察 (ID:icbank),作者:李晨光

相关推荐

韩国存储双雄,再次领先

存储芯片“寒冬”下,韩国芯片大厂仍在进攻

韩国的“5G领先”故事也讲不下去了

中国IGBT双雄的进击之路

韩国半导体新一轮“操作”见效?

台积电和联电:芯片代工双雄25年恩仇录

韩国半导体,急了?

韩国半导体怎么了?

TCL科技豪掷350亿背后野望

智能硬件“双雄”:先跑的VR何故被智能音箱反超?

网址: 韩国存储双雄,再次领先 http://www.xishuta.com/newsview85765.html

推荐科技快讯

- 1问界商标转让释放信号:赛力斯 95228

- 2人类唯一的出路:变成人工智能 21183

- 3报告:抖音海外版下载量突破1 21148

- 4移动办公如何高效?谷歌研究了 20339

- 5人类唯一的出路: 变成人工智 20338

- 62023年起,银行存取款迎来 10336

- 7五一来了,大数据杀熟又想来, 8596

- 8网传比亚迪一员工泄露华为机密 8505

- 9滴滴出行被投诉价格操纵,网约 8215

- 10顶风作案?金山WPS被指套娃 7230